Frequency Synthesiser

The frequency synthesiser has been implemented by means of a PLL. The simplified block diagram of which is shown in Figure 3-29.

The feedback loop causes both input signals of the phase frequency detector (PFD), the output of the pierce oscillator, and the output of the pulse swallow divider to lock, thereby creating a voltage controlled oscillator (VCO) output frequency (fout) multiple of the reference frequency (fXtal). The feedback loop takes part of the output signal and divides its frequency to compare the resulting signal with a reference signal. The difference between these two signals is converted into a voltage that controls the frequency of the output signal. When the divided signal is equal to the reference signal, the output is phase locked.

Figure 3-27 Montecarlo analysis simulation results for input voltage of ±7.5mV (top) and ±12.5mV (bottom) out of 200 samples

Figure 3-28 Flip-flop block diagram

Figure 3-29 Simplified block diagram of the implemented PLL

The value of the synthesised frequency at the VCO output is determined by the division factor of the frequency divider compared to the output frequency of the pierce oscillator. In the design example, the PLL must provide one of two frequencies, depending on the operation mode: 1554.69MHz or 1571.328MHz, which are set by the frequency selection pin of the pulse swallow divider.

These frequencies, as shown in Figure 3-29, are obtained by means of a pulse swallow divider, which divides the VCO output frequency by 95 in the first case and by 96 in the second case. After that, the PFD compares the resulting signal with the reference frequency of 16.638MHz, which is generated by the pierce oscillator. The output of the PFD then controls the charge pump to set the VCO tuning voltage.

Figure 3-30 Frequency synthesiser layout

The layout of the complete PLL is shown in Figure 3-30 and it occupies an area of 870×615|im2. Table 3-11 shows the required specifications and the post-layout simulation results for the PLL. The quartz crystal and loop filter are external to the integrated circuit (IC).

It can be seen that most of the requirements are fulfilled by the design example. The output power is between the specified 0dBm and 3dBm for a 50Q load, being the output power for the mixer load lower due to its impedance. The required frequency range is also covered by the PLL. Although the requirement of the KVCO is lower than specified, the PLL generates the required signal frequencies and therefore meets the standards of the application.

The power of the second harmonic is higher than specified when the control voltage is equal to 0.5V, which is also acceptable because of the narrowband characteristic of the front-end. Phase noise at the working frequency fulfils the specification of -90dBc/Hz, however with GPS and Galileo being spread spectrum systems, phase noise is not a critical issue and even a value around -83dBc/Hz at 100kHz offset is acceptable [SONY CXA1951AQ] [uNAV un8021C] [Freescale MRFIC1505] [ST STB5610] [zarlink GP2015] [Atmel ATR0603]. Finally, the resulting consumption is around 10 percent higher than specified, which was required to reach this level of performance. This will solely affect the low power consumption feature of the front-end.

TABLE 3-11 Post-layout simulation results for the PLL

|

|

Specified |

Post-layout |

|

||

|

Parameter |

[2.8V] |

[0.5V] |

[2.8V] |

[0.5V] |

Unit |

|

Output power |

0~3 |

0~3 |

1.09 |

1.26 |

dBm |

|

Frequency |

1.544 |

1.571 |

1.49 |

1.71 |

GHz |

|

Phase noise @100kHz |

-90 |

-90 |

-83 |

-97 |

dBc/Hz |

|

2. order harmonic |

-23 |

-23 |

-22.5 |

-13.2 |

dBc |

|

Current consumption |

<9 |

<9 |

10 |

10 |

mA |

The following subsections describe the different parts of the implemented PLL in detail: the voltage controlled oscillator, pulse swallow divider, phase frequency detector and charge pump, pierce oscillator, and loop filter.

Voltage Controlled Oscillator (VCO)

The VCO is the component that generates the LO input signal for the mixer at a given frequency. To have an accurate signal frequency, the VCO is controlled by a PLL, which corrects the frequency and phase differences and ensures frequency stability. Figure 3-31 shows the circuit scheme of the completely integrated differential VCO of the design example. An LC tank has been selected because of its integration abilities in comparison with other alternatives. Two cross-coupled transistors, Ml and M2, generate the negative impedance required to cancel the losses associated with the non-ideal LC tank. There are two advantages of this architecture: Use of PNP transistors is avoided and a higher control voltage tuning can be employed.

The main parameters of the output signal are frequency, amplitude, and phase noise. The VCO of the design example is built by means of a resonating LC tank. Therefore, the frequency is set by the control voltage that varied the capacitance of a resonating LC tank. The power can be determined by VCO’s coupled transistor stage gain, and impedance matching between the VCO output and the mixer input. The oscillator phase noise depends on the quality factor of the LC tank; the noise figure of the amplifier, which creates a negative resistance; and the energy in the LC tank.

Figure 3-31 Simplified scheme of the VCO

The simplest way to reduce phase noise is by increasing the resonator energy through the application of higher voltage to the tank. In the current design, an emitter-coupled pair with cross feedback is used as a negative resistance, which is responsible for the undamping of the resonator. The limit of the maximum oscillation amplitude will depend on the feedback. The easiest way to implement the aforementioned feedback is by a direct coupling: No biasing network is required and very low power consumption can be achieved (see Figure 3-31).

The LC tank sets the frequency range where the VCO will oscillate. For the LC tank, an inductor (L) and a varactor (C) are required. The main parameters of the inductor are the inductance, the self-resonance frequency, and the quality factor, whereas those of the varactor are its capacitance, quality, and tuning range.

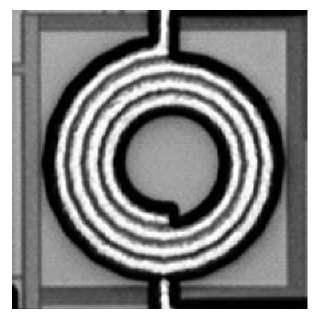

The performance of the inductor has been estimated by the spiral inductors and transformers simulator ASITIC [ASITIC], taking into account technological features such as parasitic capacitance of metal tracks and ohmic lines. A 2.5nH inductor has been designed with the fourth metal layer (low resistivity, thick metal) to reduce the ohmic lines associated and to enhance the quality factor (Q). A microphotograph of the inductor is shown in Figure 3-32.

The characteristics of the fabrication process allow the implementation of the varactor with a PN junction composed of P+ diffusion in an N-type well[Gutierrez07]. The capacitance, tuning range, and quality factor are defined by the technology, the configuration, and the size of the varactor. An interdigit varactor of 75 fingers with a length of 30|im and the minimum possible width and separation allowed by the technology has been designed for the LC tank of the VCO. The capacitance is 2.5pF for a 0.5V control voltage and 1.5pF for 2.8V, resulting in a tuning range of 26.5 percent (simulation results).

Figure 3-32 Microphotograph of the VCO inductor

Considering the inductance and capacitance previously obtained, a KVCO of 254kHz/V could be obtained for the defined tuning range. However, this value is reduced due to the parasitic capacitances of the metal lines, transistors, and so on.

The VCO consists of three main parts: the LC tank, the negative resistance loop (see Figure 3-31), and an emitter follower stage. The latter works as a buffer, driving the load of the VCO, which is the mixer and pulse swallow divider.

As previously mentioned, the negative resistance loop compensates the losses of the LC tank to maintain stable oscillation; it consists of two cross-coupled transistors, as shown in Figure 3-31. Therefore, it could be thought that the value of the transconductance should be the same as the resistive part of the LC tank. However, this would not ensure oscillation. Therefore, a security factor between 2 and 3 has to be considered, as stated in[Craninckx-Steyaert98]. The selection of this security factor is a trade-off between the current consumption of the VCO and the risk of VCO oscillation failure due to process variation. In the design example, a security factor of 2 has been applied.

The post-layout results shown in Table 3-12 have been obtained by means of simulations.

The results meet most of the requirements. As explained for the PLL, the power of the second harmonic is higher than specified for the case of the control voltage being equal to 0.5V. This is acceptable because of the narrowband characteristic of the front-end. With Galileo and GPS being spread spectrum systems, phase noise is not a critical issue. Even a value around -83dBc/Hz at 100kHz offset is acceptable [SONY CXA1951AQ] [uNAV un8021C] [Freescale MRFIC1505] [ST STB5610] [zarlink GP2015] [Atmel ATR0603]. Phase noise postlayout simulation results showed that this requirement is fulfilled at the working frequencies of the PLL, although at the highest frequencies of the VCO’s frequency is lower than specified, this is acceptable for a spread spectrum system as explained previously. Finally, the frequency tuning is slightly lower than specified, but required working frequencies of 1554.69MHz and 1571.328MHz are within the required frequency range.

TABLE 3-12 VCO post-layout simulation results

|

Corner |

Vctr [V] |

Pout [dBm] |

Fout [GHz] |

Freq. Tuning [%] |

2.harm. Power [dB] |

2.harm. Fout [GHz] |

Noise @ 100k [dBc/Hz] |

Current [mA] |

|

Spec. |

0.5 |

0-3 |

1.717 |

±10 |

-23 |

-90 |

<6 |

|

|

2.8 |

1.408 |

|||||||

|

0.5 |

1.26 |

1.71 |

-13.25 |

3.43 |

-81.2 |

|||

|

Sim. |

2.8 |

1.09 |

1.49 |

±6.96 |

-22.55 |

2.98 |

-96.9 |

6.3 |