Information Technology Reference

In-Depth Information

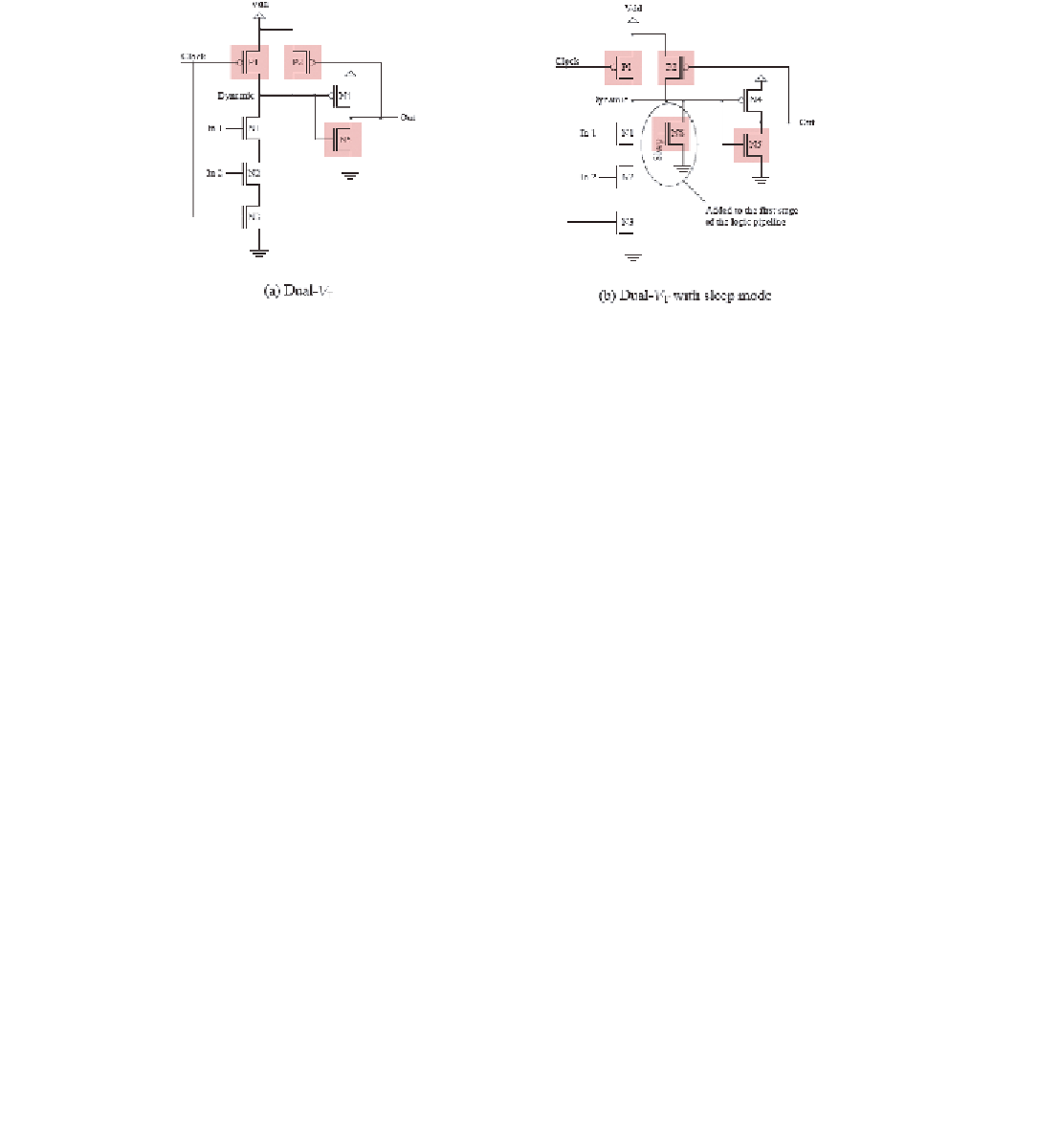

FIGURE 5.21:

Low-leakage dual-

V

T

AND gate (a) and same with sleep mode (b). In (a) P1, P2, and

N5 are high-

V

T

devices (they are not on the critical path for evaluation). In (b) the NS high-

V

T

transistor

is the “sleep” transistor that discharges the dynamic node. Reproduced from [

69

]. Copyright 2002 IEEE.

leakage paths in dynamic domino logic depend on the state of the internal dynamic nodes. This

property is exploited for the implementation of a sleep mode specific to domino logic.

The low-leakage domino logic is built using dual-

V

T

devices according to the MTCMOS

design methodology described above. By selectively using high-

V

T

devices in the non-critical

paths, performance is not compromised. Figure 5.21 shows the integration of high-

V

T

devices

(shaded transistors) in the domino-logic AND gate. Evaluation speed is not affected by this

configuration.

However, an asymmetry in the leakage currents is created. This asymmetry depends on

the voltage level at the internal dynamic node. If either input is low, the dynamic node remains

charged, resulting in a large subthreshold leakage current through the high-leakage transistors

N1, N2, N3, and N4. But, when the dynamic node is discharged, the low leakage transistors

P1, P2, and N5 are strongly cutoff and the leakage in the whole circuit is dramatically reduced.

Thus, to put a dynamic domino circuit in a low-leakage state, all that is needed is

to discharge its dynamic nodes (and of course clock-gate it to prevent them from getting

recharged). This can only be done if the circuit is idle since in the low-leakage state it cannot

evaluate its inputs—it first needs to be recharged. This is a distinct technique, for a low-leakage

state, from the power gating techniques presented in Section 5.2.6 or from ordinary clock gating

for dynamic power.

Similarly to switching on and off the sleep transistor in the power-gating techniques

(Section 5.2.6), discharging the dynamic nodes of a domino circuit carries an energy penalty.

The energy cost is proportional to the number of nodes discharged to enter the sleep mode. As

Search WWH ::

Custom Search