Information Technology Reference

In-Depth Information

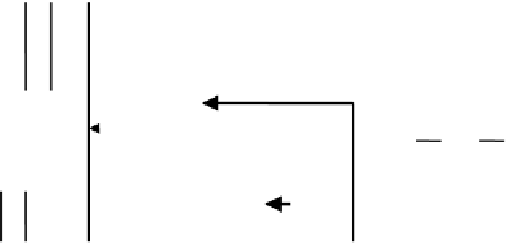

Figure 10.4 RISC four-bus organization

(OD), Operand Store

Execution (OS

/

EX), and Operand Fetch (OF). The first three

stages perform respectively instruction fetch, instruction decode, and operand fetch.

The OS

/

EX stage sends operand to memory in the case of a store instruction or use

the ALU in case of instruction execution. The OF stage receives the operand in case

of a load instruction. MIPS uses a mechanism called pipeline interlock in order to

prevent an instruction from continuing until the needed operand is available.

Unlike the Berkeley RISC, MIPS has a single set of sixteen 32-bit general-

purpose registers. The MIPS compiler optimizes the use of registers in whatever

way is best for the program currently being compiled. In addition to the 16 general-

purpose registers, MIPS provided four additional registers in order to hold the four

previous PC values (to support backtracking and restart in case of a fault). A fifth reg-

ister is used to hold the future PC value (to support branch instructions).

Four addressing modes are used in MIPS. These are immediate, indexed, based

with offset, and base shifted. Four instruction groups were identified in MIPS.

These are ALU, Load

/

Store, Control, and Special instructions. A total of 13 ALU

instructions were provided. These include all register-to-register two- or three-

operand formats (Fig. 10.5). A total of 10 LOAD

/

STORE instructions were pro-

vided. They use 16 or 32 bits. In the latter case, indexed addressing is used by

adding a 16-bit signed constant to a register using the second format in

Figure 10.5. A total of six control flow instructions were provided. These include

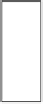

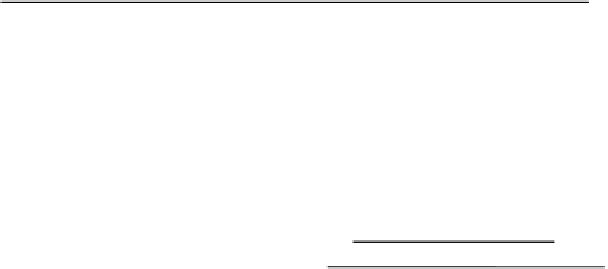

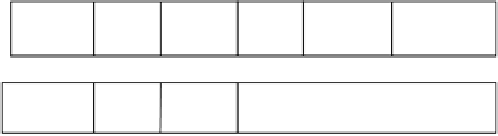

/

6

5

5

5

5

6

Op-Code

SRC 1

SRC 2

DST

SHIFT

Function

6

5

5

16

Op-Code

SRC

DST

Immediate Constant

Figure 10.5 Three-operand instructions used in MIPS

Search WWH ::

Custom Search