Information Technology Reference

In-Depth Information

P

1

P

2

Data

(

bit)

line b

Data (bit)

line b

N

3

N

4

B

A

N

2

N

1

Word sele ct lin e

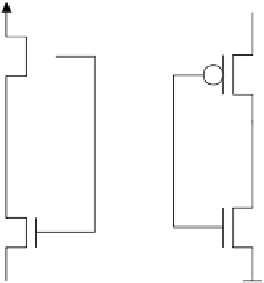

Figure 7.3 Static CMOS memory cell

one can show that if A

¼

1, which represents the other cell stable state,

call it state 0. The two transistors N

3

and N

4

are used to connect the cell to the two

data (bit) lines. Normally (if the word select is not activated) these two transistors are

turned off, thus protecting the cell from the signal values carried by the data lines.

The two transistors are turned on when the word select line is activated. What takes

place when the two transistors are turned on will depend on the intended memory

operation as shown below.

0, then B

¼

Read operation:

1. Both lines b and b are precharged high.

2. The word select line is activated, thus turning on both transistors N

3

and N

4

.

3. Depending on the internal value stored in the cell, point A(B) will lead to the

discharge of line b(

b).

Write operation:

1. The bit lines are precharged such that b(

¼

1(0).

2. The word select line is activated, thus turning on both transistors N

3

and N

4

.

3. The bit line precharged with 0 will have to force the point A(B), which has

1, to 0.

b)

The internal organization of the memory array should satisfy an important

memory design factor, that is, efficient utilization of the memory chip. Consider,

for example, a 1K

4 memory chip. Using the organization shown in Figure 7.2,

the memory array should be organized as 1K rows of cells, each consisting of

four cells. The chip will then have to have 10 pins for the address and four pins

for the data. However, this may not lead to the best utilization of the chip area.

Search WWH ::

Custom Search