Information Technology Reference

In-Depth Information

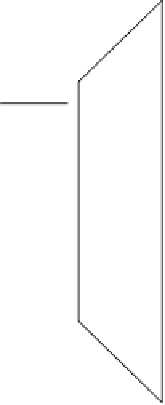

CPU

Main Memory

n

b

n lines

0

1

2

A

0

−

A

n

−1

MAR

b

b lines

D

0

−

D

b

−1

MDR

R / W

2

n

−

1

Figure 7.1 A typical CPU and main memory interface

In static CMOS technology, each main memory cell consists of six transistors as

shown in Figure 7.3. The six transistor static CMOS memory cell consists of two

inverters back to back. It should be noted that the cell could exist in one of the

two stable states. For example, if in Figure 7.3 A

¼

1, then transistor N

2

will be

on and point B

¼

0, which in turn will cause transistor P

1

to be on, thus causing

point A

¼

1. This represents a cell stable state, call it state 1. In a similar way

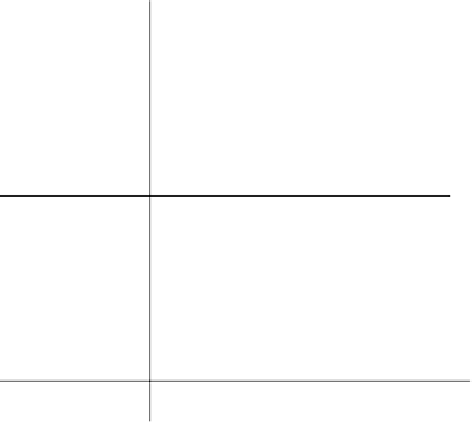

Cell

Cell

Cell

W

0

A

0

W

1

A

1

W

2

A

2

·

·

·

·

·

·

A

n - 1

W

2

n

- 1

Data Lines

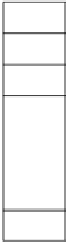

Figure 7.2 A conceptual internal organization of a memory chip

Search WWH ::

Custom Search