Information Technology Reference

In-Depth Information

to process variation. In [5], a Fine and Coarse Block architecture is proposed

to reduce number of delay stages required in a Vernier Delay Line (VDL) based

architectures. However, since the delay range in each block is constant, a large

number of stages are still required to measure path delays over a wide range.

In [6] and [2], delay range of each stage in a VDL based design increases by

a factor of two. Such a delay range allows measurement of delay over a wide

dynamic range with reduced area overhead as compared to previous designs.

However, for a wide range of delay measurement, size of buffer increases expo-

nentially, which increases the area overhead.

Motivated by the results of a variable delay range in VDL architecture, a

VDL based design is proposed in which the delay range in each stage depends

on a crossover. After a crossover, delay range of subsequent stages is reduced

and the signal transition which occurs earlier is delayed more than the other

signal transition. This reduces the number of buffers used in each stage and also

enables a wide range delay measurement.

2 Proposed Architecture

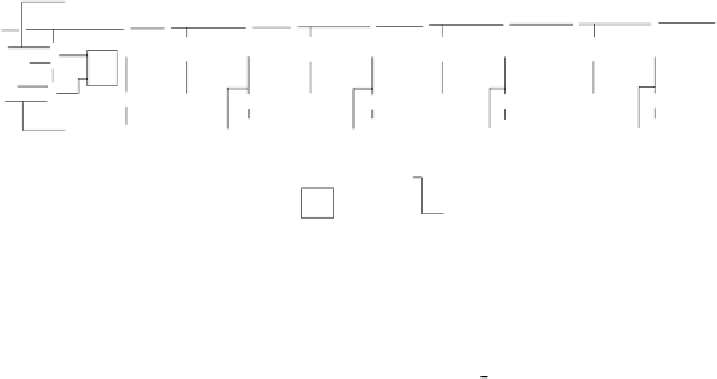

Proposed architecture consists of delay stages and every delay stage has D flip

flop (DFF), multiplexers, Buffers (BUFs) and Programmable Delay Elements

(PDEs), as shown in Figure 1 . Input and output of the Path Under Test (PUT)

are connected to START1 and STOP1, respectively.

PDE_U

PDE_U

PDE_U

PDE_U

PDE_U

BUF

BUF

BUF

BUF

BUF

STOP 2

STOP 3

STOP 4

STOP5

STAGE 2

STAGE 3

STAGE 5

STAGE 1

STAGE 4

SEL

STOP 1

D

CLK

D

Q2

CLK

D

CLK

D

CLK

D

CLK

Q1

Q3

Q4

Q5

0

SCLK

SCLK

SCLK

SCLK

SCLK

START 1

START 3

START 2

START 4

START 5

BUF

BUF

PDE_D

BUF

PDE_D

BUF

PDE_D

BUF

PDE_L

PDE_L

1

1

1

Latch

Latch

Latch

Latch

Latch

Latch

Set

Reset

Set

Reset

Reset

Set

Fig. 1.

Proposed architecture with variable delay range to measure path delay

Input signals to an

i

th

delay stage are represented by STARTi and STOPi,

which are delayed form of START1 and STOP1, respectively. STARTi passes

through lower delay chain comprising of either a PDE LorPDEDandaBUF.

STOPi passes through upper delay chain, which comprises of PDE UandaBUF.

In

i

th

delay stage, STARTi signal and STOPi signal are connected to the clock

port and data port of DFF, respectively. The output of DFF is denoted by Qi,

where i denotes the stage index. DFF of all the stages are initially reset to zero.

Output of DFF indicates the signal transition which occurs earlier in a delay

stage, as shown in the Figure 2 .