Information Technology Reference

In-Depth Information

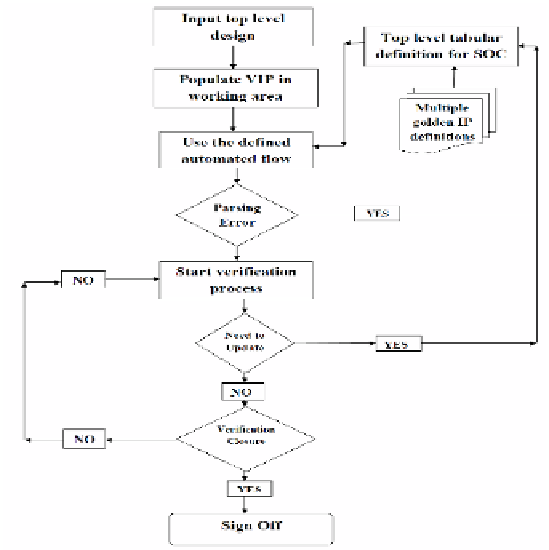

Fig. 2.

Flow at SoC Level

This completes the information which is needed from the user side. Based on the

above information given, tool will deliver a fully functional UVM based testbench.

Flow and working of tool:

Given the name of VIP, first it will look whether it is existing or non-existing. For

existing ones, the tool will populate it from the central repository otherwise it will

create complete VIP based on UVM which includes transaction item, sequence,

sequencer, driver, monitor and agent. Now all the VIP blocks which were defined are

in working area along with the top level design. The VIP instances will be

automatically connected to DUT based on the tabular information specified.

The interface definition using

uvm_config_db::set

will also be done so that

lower level verification components will automatically get access to interface using

uvm_config_db::get

operation. Now the Environment class will be created which will

instantiate different agents, build and connect them. Also tool has different sequences

for each VIP which completes the requirement for creating a top level testbench class.

Finally a UVM based testbench will be developed which will inherit environment and

different sequence class. Different components will be built, configuration of

VIP will be done and sequences will start on respective sequencer in run phase.

Based on simulator choice, testbench will be simulated with proper command line

arguments.