Information Technology Reference

In-Depth Information

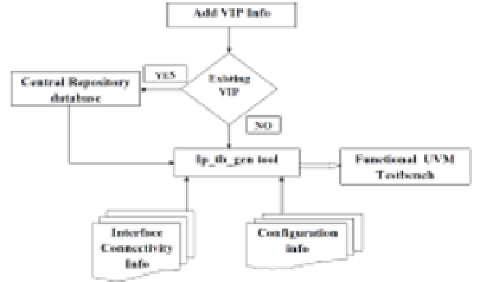

Fig. 3.

Architecture of Tool

From the user's perspective both standard methodology and verification language

i.e. UVM and System Verilog is used. So no extra learning is required in order to

deploy this tool and methodology. Figure 3, explains the architecture of the tool. The

inputs of the tools are mostly VIP definitions while the output is UVM based

testbench. The tool also has the facility for creating VIP's which are non-existing,

further which will be kept in central repository database.

5

Case Study

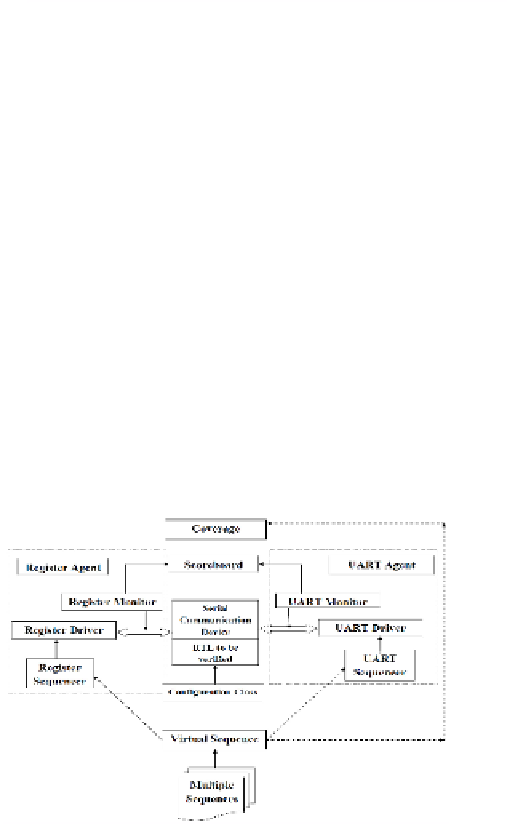

The ip_tb_gen tool methodology was applied for block level verification of IP based

on Serial Communication Interface. The following section will make clear the

understanding of both tool and methodology. For this UVM based testbench

architecture is shown in Figure 4.The top level design is based on Serial

Communication. There are four different VIP's namely UART, Register access,

Clock driver and Interrupt Handler. Out of these Interrupt handler and clock driver

Fig. 4.

Reference testbench architecture