Hardware Reference

In-Depth Information

Table 3.12

Instruction set for

arithmetic cells

Type

Operations

Arithmetic operation

[ MLT ] ACC[S;signed/U;unsigned] (accumulation)

[ALU] ADD, ADDC(with carry) (addition)

[MLT] ADDSAT[S/U], ADDSAT[S/U]C (addition)

[MLT] ADDSUB (addition and subtraction)

[MLT] MAC[S/U], MACSU, MACUS (multiply and

accumulation)

[MLT] MULC[S/U], MUL[S/U], MULSU, MULUS (multiply)

[ALU] SUBB, SUB (subtraction)

(supports 16-bit data with no suffix and 8-bit data with suffix of .B)

Logical operation [ALU]

AND, NOT, OR, RED (reduction), XOR

(supports 16-bit, 8-bit, and 1-bit data with suffix of .C except

for reduction)

Shift operation [ALU]

EXTS (sign extension), EXTU (zero extension)

ROTL, ROTR (rotation), ROTCL, ROTCR (rotation with carry)

SHAL, SHAR (arithmetic shift), SHLL, SHLR (logical shift)

SWAP (swap)

(supports 8-bit and 1-bit data for extension and swap, 16-bit

data for rotation and shift)

Data control [ALU/MLT]

NOP (no operation), STC (immediate value store)

THR (data forwarding)

(supports 16-bit, 8-bit, and 1-bit data)

Flow control [ALU]

CNT (count), GATE (data forwarding with condition)

GES, GEU, GTS, GTU (comparison)

JOIN (join), MUX (multiplexing), TEST (equal comparison)

(supports 16-bit and 8-bit data)

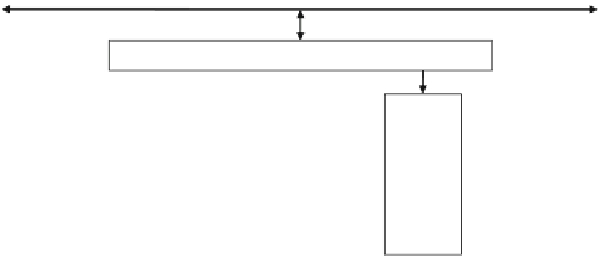

Cell control bus

From/To

crossbar

(Port 0)

Operation cell control / Configuration control

×

4

To local memory

(Port 0)

Write control

Read control

Memory

I/F

(Port 0)

×

4

Write control

Read control

Bus

I/F

Write control

Read control

To local memory

(Port 1)

From/To

crossbar

(Port 1)

Write control

Read control

Memory

I/F

(Port 1)

×

4

×

4

1-bit data (carry) with a valid bit

8-bit data with a valid bit

Fig. 3.51

Block diagram of load-store (LS) cell

Search WWH ::

Custom Search