Hardware Reference

In-Depth Information

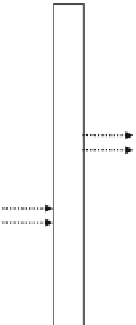

Cell control bus

Operation cell control / Configuration control

ALU

Arithmetic op.

Logical op.

Flow control

From four

neighboring

cells

To four

neighboring

cells

SFT

Shift op.

×

4

THR

Data control

×

4

1-bit data (carry) with a valid bit

8-bit data with a valid bit

Fig. 3.49

Block diagram of arithmetic operation (ALU) cell

3.2.2

Arithmetic Blocks

The 8 × 4 2D operation-cell array consists of two types of cells: 24 arithmetic oper-

ation (ALU) cells that mainly execute arithmetic, logical, and shift operations and

8 multiplication (MLT) cells that mainly execute multiplication, multiply-and-

accumulation operations. Figures

3.49

and

3.50

show block diagrams of the ALU

cell and the MLT cell, respectively. The number of data inputs and outputs is the

same in all of the cells. The position of the MLT cells is selectable in either the first

or second row from the left. Every cell is connected only to its four neighboring

cells; therefore, the FE-GA can operate at a high frequency due to its short-distance

wiring. Calculations and data transfers are executable simultaneously. Consequently,

data can be transferred without lowering the operation efficiency by relaying on

multiple cells.

The ALU and MLT cells are equipped with operation units, operand-delay regis-

ters for input data and accumulation, output registers, and configuration control

logics that cooperate with the sequence manager and configuration manager placed

outside the cell array. The three operation units of the ALU cells include an ALU

unit executing arithmetic operations, logical operations and flow controls, an SFT

unit executing shift operations, and a THR unit executing data controls. The two

operation units of the MLT cells include a MAC unit executing multiplication,

Search WWH ::

Custom Search