Hardware Reference

In-Depth Information

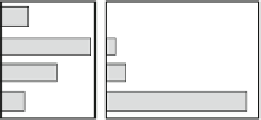

SH-3E

0.5

µ

m

1.0

1.0

1.0

0.25

µ

m

5.1

4.6

1.1

SH-4

x 2.2

0.18

µ

m

5.1

3.6

1.4

0.13

m

SH-X

µ

13

4.2

3.1

0

4

8

12

01

23

0 2 4 6 8

Architectural

Performance

Relative

power

Architectural

power performance ratio

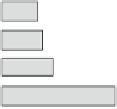

SH-3E

0.5

m

0.97

600

1.6

µ

0.25

m

0.18

µ

m

0.13

µ

10

2000

5.0

SH-4

x 7.3

12

1200

10

µ

m

SH-X

36

500

73

0 0 0 0

Performance

(M polygons/s)

0

1000

2000

0 0 0 0 0

Power

(mW)

Power performance ratio

(M polygons/s/W)

Fig. 3.41

Power ef fi ciencies of SH-3E, SH-4, and SH-X

3.1.7

Multicore Architecture of SH-X3

Continuously, the SH cores achieved high efficiency as described above. The SH-X3

core was developed as the third generation of the SH-4A processor core series to

achieve higher performance with keeping the high-efficiency maintained in all the

SH core series.

The multicore architecture was the next approach for the series. In this section,

the multicore support features of the SH-X3 are described, whereas the multicore

cluster of the SH-X3 and a snoop controller (SNC) are described in the chip imple-

mentation sections of RP-1 (Sect. 4.2 ) and RP-2 (Sect. 4.3 ).

3.1.7.1

SH-X3 Core Speci fi cations

Table

3.9

shows the specifications of an SH-X3 core designed based on the SH-X2

core (see Sect.

3.1.4

). The most of the specifications are the same as that of the

SH-X2 core as the successor of it. In addition to such succeeded specifications, the

core supports both symmetric and asymmetric multiprocessor (SMP and AMP) fea-

tures with interrupt distribution and interprocessor interrupt, in corporate with an

interrupt controller of such SoCs as RP-1 and RP-2. Each core of the cluster can be

set to one of the SMP and AMP modes individually. It also supports three low-power

modes of light sleep, sleep, and resume standby, which can be different for each

core as the operating frequency can be. The size of the RAMs and caches is flexible

depending on requirements in the range as shown in the table.

Search WWH ::

Custom Search