Hardware Reference

In-Depth Information

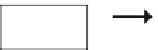

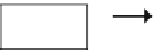

I

T

Bus Bridge

Initiator

Core #0

I

T

T

SHPB

Targ et

I

T

Core #1

T

CSM

T

SRAM i/f

I

T

600MHz

32 bits

Core #2

T

DDR2 i/f

I

T

300MHz

(I-to-T: 3.3ns)

Core #3

64 bits

,

2.4GB / s

I

T

I - to -T Connection

SNC

29-bit Address

(Request)

64-bit Data

(Request)

I

T

Debug

64-bit Data

(Response)

Fig. 4.7

SuperHyway connection of IPs including SH-X3 cluster

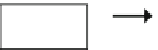

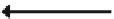

Fig. 4.8

Physical

organization of SuperHyway

connection

Core #0

Core #1

Router

Core #3

Core #2

1 mm

IP address and ends at many F/Fs of target HW-IPs. The 300 MHz 64-bit SuperHyway

achieved the throughput of 2.4 GB/s, which is the same throughput as the 600 MHz

32-bit DDR2 interface.

Figure

4.8

shows the physical organization of the interconnect logic, where each

arrow includes 29-bit-address and 128-bit-data lines corresponding to Fig.

4.7

. The

routing block was synthesized as a net list without actual wire lengths. A long wire

path caused an unacceptable CR delay that could be calculated after place and route,

so we inserted repeater cells to improve the path delay. As a result, a one-cycle path

from an initiator to a target could reach the shaded area.

Figure

4.9

shows the chip micrograph of the RP-1. The chip was integrated in

two steps to minimize the design period of the physical integration, and successfully

fabricated: (1) First, a single core was laid out as a hard macro and completed

Search WWH ::

Custom Search