Hardware Reference

In-Depth Information

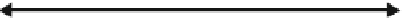

R1 G1

R2 G2

R3 G3

D1

D2

D

3

42 cycles, 52% External Bus Utilization

R1,R2,R3: Requests

G1,G2,G3: Grants

D1,D2,D3: External Bus Accesses

(i) Non Split Bus Transactions

R1 G1

R2 G2

R3 G3

D1

D2

D3

30 cycles, 80% External Bus Utilization

(ii) Split Bus Transactions

Fig. 4.6

Improvements in utilization ratio achieved in split bus transaction

must also be flexible to support different configurations. The SuperHyway can

perform two routing jobs at any instant. It can receive data transaction requests from

HW-IP-module initiator ports and route one of the requests to the target port of a

HW-IP module that is ready to receive the transaction request. At the same time, it

can route a response from the target port. Such a response might be “Read data on

read transaction request.” The response is automatically directed back to the origi-

nal initiator port. Target ports can receive requests and save them in an internal

service queue.

The upper eight bits of the 32-bit address are used to specify a module connected

to the SuperHyway, and a multiple of 16-MB spaces are assigned to each module.

Then an initiator can access any location mapped on the 4-GB address space.

A request packet has a field consisting of an 8-bit transaction ID so that SuperHyway

modules can initiate 256 outstanding transactions. A module can request a transac-

tion after the previous transaction is granted by the SuperHyway. This split transac-

tion effectively hides the long latency of a slow response such as an external memory

access or peripheral module access. As a result, the bus utilization ratio is highly

improved. Figure

4.6

compares how a non-split transaction bus and the SuperHyway

access an external DRAM. The utilization ratio is improved by 28% for this case.

4.2.6

Chip Integration

The RP-1 integrated lots of HW-IPs, and a flat interconnection by a single

SuperHyway was not feasible. We connected the HW-IPs together including the

SH-X3 cluster with one SuperHyway and connected them to the other HW-IPs via

bus bridges. Figure

4.7

illustrates the connection. Ten HW-IPs and a bridge are con-

nected within a single SCLK cycle. “I” and “T” indicate initiator and target ports.

A SuperHyway routing block connects these ports for the single-cycle transfer

among the HW-IPs at 300 MHz. The critical timing path starts at an F/F of an initiator

Search WWH ::

Custom Search