Hardware Reference

In-Depth Information

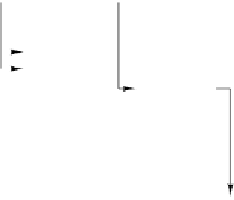

The OMAP4430 ARM CPU virtual memory mapping accommodates four

page sizes. Page sizes of 1 MB and 16 MB are mapped with a page descriptor lo-

cated in the first-level descriptor table. There is no need for second-level tables in

this case, as all of the entries would point to the same large physical page. The

64-KB pages descriptors are located in the second-level descriptor table. Because

each entry of the second-level descriptor table maps 4 KB of virtual address page

to a 4-KB physical address page, 64-KB pages require 16 identical descriptors in

the second-level descriptor table. Now why would any sane OS programmer

declare a page as 64 KB in size when the same space would be required to map the

page to more flexible 4-KB pages? Because, as we will see shortly, 64-KB pages

require fewer TLB entries, which are a critical resource to good performance.

Nothing slows a program down more than a constricting memory bottleneck. If

you were keeping score in Fig. 6-18, you probably noticed that for every program

memory access two additional memory accesses are required for address transla-

tion. This 200% overhead in memory accesses for virtual address translation would

bring any program to a crawl. To avoid this bottleneck, the OMAP4430 ARM CPU

incorporates a hardware table called a

TLB

(

Translation Lookaside Buffer

) that

quickly maps virtual page numbers onto physical-page-frame numbers. For the

4-KB page size, there are 2

20

virtual page numbers, which is over 1 million. Clear-

ly, not all of them can be mapped.

Page table (walked by MMU on TLB misses)

TLB (MMU hardware)

1

st

level page

table index

2

nd

level

table index

Offset

ASID

Virtual

page

Flags

12 bits

8 bits

12 bits

Physical

page

TTBR

Valid

1

st

level

descriptor

table

2

nd

level

descriptor

table

20 bits

Physical page address

Offset

(a)

(b)

Figure 6-18.

Data structures used in translating virtual addresses on the

OMAP4430 ARM CPU. (a) Address translation table. (b) TLB.

Instead, the TLB holds only the most recently used virtual page numbers. In-

struction and data pages are kept track of separately, with the TLB holding the 128

most recently used virtual page numbers in each category. Each TLB entry holds a

virtual page number and the corresponding physical page-frame number. When a

process number, called an

address space identifier

(ASID), and a virtual address