Hardware Reference

In-Depth Information

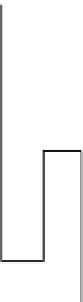

V

DD

a

c

: load transistor

: control transistor

: diffusion

: metallization

: contact

metallization-diffusion

a

b

b

c

d

d

V

SS

Fig. 8.7

Rules for opens at gate level

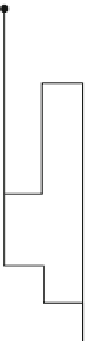

V

DD

V

DD

V

DD

e

c

c

f

d

d

a

c

a

b

d

b

2

a

e

b

e

f

f

V

SS

V

SS

V

SS

Fig. 8.8

Rules for shorts at gate level

number 4 is physically possible but with the second this open is no longer feasible

and, in this latter case, all opens can be modeled by stuck faults of either the output,

or one or more inputs of the gate.

A similar reasoning applies to the only type of

short

that cannot be modeled

two prevent its occurrence either because the diffusions concerned are separated by

the output diffusion or simply because they are more separated physically. It is also

worth pointing out that for the two latter layouts, any short can also be modeled by

a stuck-at fault of either the output, or one or more inputs.

According to the whole set of rules concerning the connections within the gates

therefore consist of arranging these connections so that any defect can be modeled

by a stuck-at fault.