Hardware Reference

In-Depth Information

4.3.4

Experimental Results

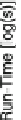

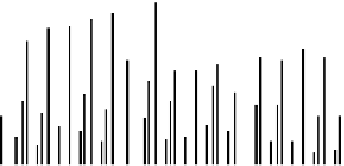

Figure

4.4

compares the run times of SUPERB in PPSFP mode, SUPERB in

SPPFP mode and the interval-based simulator, respectively. The fault list consists

of randomly selected RBFs; their number equals the number of gates in a design

multiplied by ten (this value was chosen to be close to typical numbers of realistic

faults obtained by layout analysis). Apart from this modification, the experimental

setup corresponds to that in the previous section. All experiments have been per-

formed on the same 2.8 GHz Opteron Linux machine with 16 GB RAM. SUPERB

in PPSFP mode is approximately ten times faster than SUPERB in SPPFP mode

and approximately 800 times faster than the interval-based simulator. SUPERB

also outperforms earlier resistive bridging fault simulators

0;0

by several orders of

magnitude.

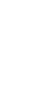

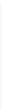

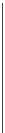

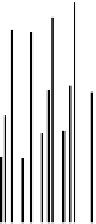

Tab le

4.3

reports the application of SUPERB to simulate large industrial circuits

provided by NXP under 10,000 test patterns. For four largest circuits, the

E-FC

computed by SUPERB and its run time in PPSFP mode is given. In addition, the

outcome of stuck-at fault simulation using the same simulation engine is reported.

The final row contains average results for 18 NXP circuits. It can be seen that SU-

PERB can process multi-million gate designs in reasonable time (the largest time is

approximately 8 h for the 2.5-million gate circuit p2921k). Preprocessing, i.e., hash

Fig. 4.4

Performance of SUPERB compared to the interval-based simulator (

logscale

)

Tabl e 4. 3

SUPERB results for combinational cores of industrial circuits provided by NXP

Circuit

Gates

RBFs

E-

FC

Time

s-a faults

s-a FC

Time (s)

p388k

506,034

5,060,340

98.87

2,265.90

881,417

96.06

71.84

p951k

1,147,491

11,474,910

99.01

4,628.91

1,557,914

95.32

127.63

p1522k

1,193,824

11,938,240

93.26

15,874.83

1,697,662

80.91

287.23

p2927k

2,539,052

25,390,520

96.57

27,852.22

3,527,607

88.56

1,100.29

Average

(18 NXP

circuits)

94.29

6,580.10

85.90

412.63