Hardware Reference

In-Depth Information

IC

LC

CC

Clock

SE

TMC

Fig. 3.23

DTS flip-flop operation

f

Y

a

e

h

2B

m

3A

1A

j

p

i

3B

b

c

n

g

Z

2A

k

1B

d

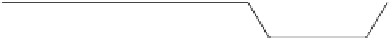

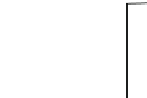

Fig. 3.24

An example to illustrate higher fault coverage using multiple scan enables

3.3.2

Multiple Scan Enable Signals

As noted earlier delay fault coverage using LOC test method are typically lower than

the coverage obtained using LOS test method. In order to increase fault coverage us-

ing LOC tests use of multiple scan enable signals was investigated in

Devtaprasanna

et al. (

2005

). The following example from

Devtaprasanna et al.

(

2005

) illustrates

how some faults not detected using a single scan enable are detected using multiple

scan enable signals.

is untestable using the LOC test method since the initialization condition a

D

d

D

1

implies h

D

1 during the launch cycle. Thus the fault effect is blocked from being

propagated to flip-flop 1A during the capture cycle. Similarly, the line n STR TDF

is LOC untestable. Next, assume that there are two scan enable signals SEN

1

and

SEN

2

with SEN

1

connected to flip-flops 1A, 2A, 1B and 2B and SEN

2

connected to

flops in the two scan chains during initialization (IC), launch (LC) and capture (CC)