Hardware Reference

In-Depth Information

a

SIN_A

SO_

A

1A

2A

3A

SEN

1

SO_

B

SIN_B

1B

2B

3B

SEN

2

b

IC

LC

CC

clock

SEN

1

SEN

2

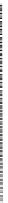

c

1A

2A

3A

1B

2B

3B

IC

X

0

X

1

X

1

LC

1

X

0

0

1

0

CC

0/1

X

X

0

0

0

Fig. 3.25

Circuit of Fig.

3.24

with two scan enable signals

cycles required to test line g STF fault. Initialization vector (1A, 2A, 3A, 1B, 2B,

3B)

D

(X,0,X,1,1,X)(X

D

don't care) is scanned in with both the scan enables

SEN1 and SEN2 set to 1. Both flip-flops 1B and 2B are initialized to 1 to set line

g to 1. Then the scan enable signal SEN1 is switched to 0 before the launch and

capture clocks are applied while SEN2 is held at 1 throughout this test. Assume that

cycles. During the launch cycle flip-flops 1B and 2B are set to 0 and a 1

!

0

transition is launched at the fault site. If an STF fault exists on g, then the value of

line g will be 1 during the capture cycle instead of 0. Since SEN2

D

1, flip-flop 3A

receives its launch cycle value (0) from flip-flop 2A instead of through its functional

data input. Therefore the fault effect is propagated to flip-flop 1A during capture

cycle and captured since SEN1 is 0. Similarly line n STR fault can be detected if

SEN1

D

0 and SEN2

D

1 during the launch and capture cycles. Thus both the LOC

untestable TDFs can be tested using two independent scan enable signals instead of

one scan enable signal.

In the test discussed above the scan enable signals are held constant at 1 or 0

during the launch and capture cycles and hence they do not need to switch fast. Also