Hardware Reference

In-Depth Information

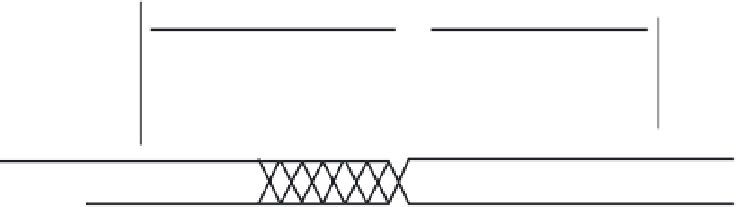

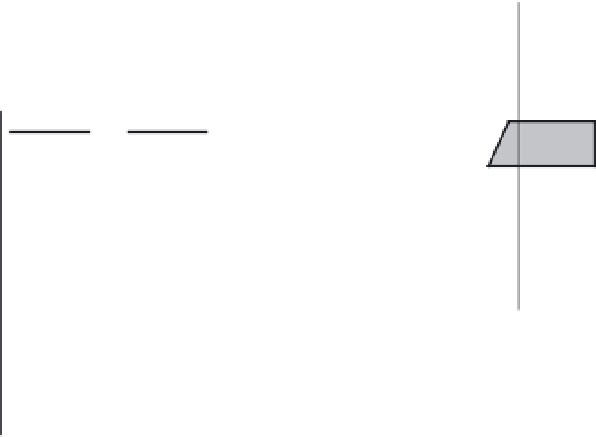

t

RC

Address

t

AA

t

OH

Data

Previous valid data

Valid data

(a) Read cycle 1 (OE and CE are asserted in the whole cycle)

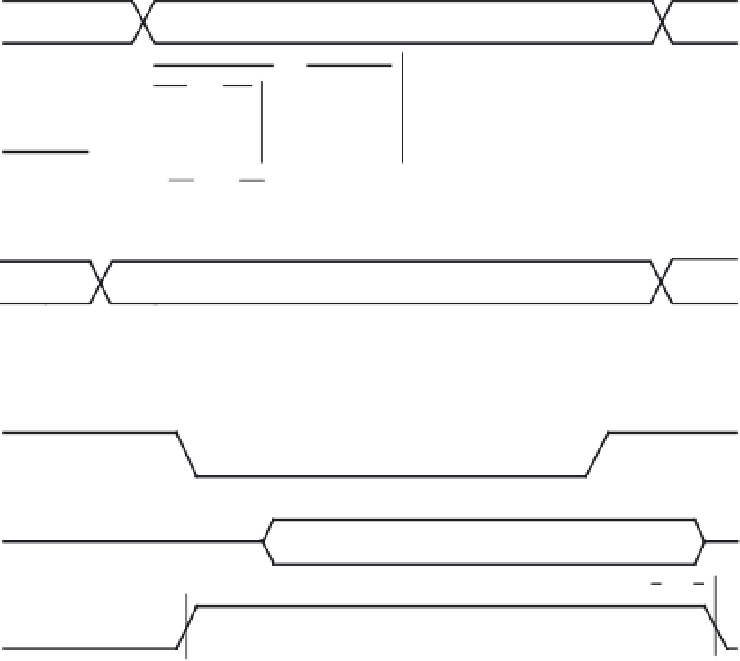

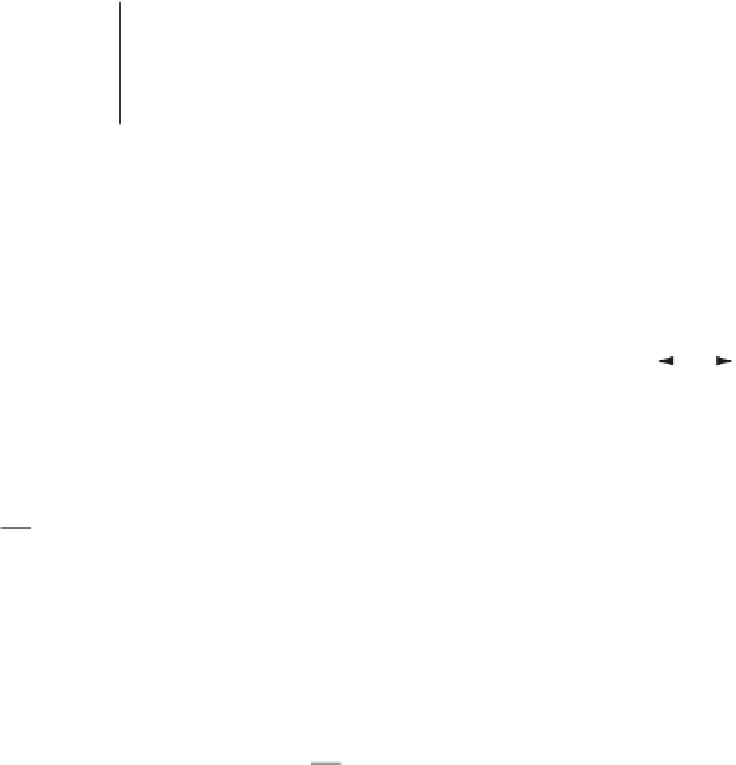

t

RC

Address

t

AA

t

CO

t

HZ

(3,4,5)

CS

t

OE

t

OHZ

OE

t

DH

t

OLZ

Data

Valid data

t

LZ(4,5)

t

PD

V

CC

t

PU

50%

50%

current

(b) Read cycle 2 (OE controlled)

Notes:

1. WE is high for read cycle.

2. All read cycle timing is referenced from the last valid address to the first

transition address.

3.

t

HZ

and

t

OHZ

are defined as the time at which the output achieves the open

circuit condition and are not referenced to the

V

OH

or

V

OL

level.

4. At any given temperature and voltage condition,

t

HZ

(max) is less than

t

LZ

(min) both for a given device and from device to device.

5. Transition is measured ±200 mV from steady-state voltage with load. This

parameter is sampled and not 100% tested.

6. Device is continuously selected with CS =

V

IL

.

7. For common I/O applications, minimization or elimination of bus contention

conditions is necessary during the read and write cycle.

Figure 14.36

■

K6R1008C1D read cycle timing diagram

Search WWH ::

Custom Search