Hardware Reference

In-Depth Information

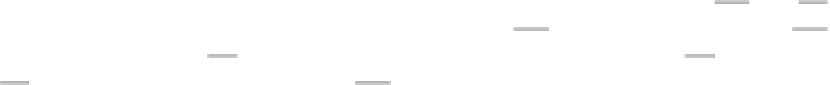

1

32

A0

A16

2

31

A1

A15

3

30

A2

A14

4

29

A3

A13

5

28

CS

OE

6

27

I/O1

I/O8

7

26

I/O7

I/O2

8

25

V

CC

V

SS

K6RC1008C1D

9

24

V

SS

V

CC

10

23

I/O3

I/O6

11

22

I/O5

I/O4

12

21

WE

A12

13

20

A4

A11

14

19

A5

A10

15

18

A9

A6

16

17

A8

A7

Figure 14.35

■

The K6R1008C1D pin assignment

low. We see that the data out gets out of the high-impedance state

t

OW

ns after the WE and CS

signals go to high. The write cycles in Figure 14.37a and b are WE-controlled because the WE

signal is asserted later than the CS signal. The write cycle in Figure 14.37c is CS-controlled

because the CS signal is asserted later than the WE signal.

The AT28C010 is a 128K 3 8 electrically erasable, programmable, read-only memory.

It needs only a 5-V power supply to operate and achieves access times ranging from 120 to

200 ns.

The AT28C010 supports a page-write operation that can write from 1 to 128 bytes. The

device contains a 128-byte page register to allow writing up to 128 bytes simultaneously.

During a write cycle, the address and 1 to 128 bytes of data are internally latched, freeing the

address and data bus for other operations. Following the initiation of a write cycle, the device

will automatically write the latched data using an internal control timer. The end of an inter-

nal write cycle can be detected by polling the I/O7 pin or checking whether the I/O6 pin has

stopped toggling.

Search WWH ::

Custom Search