Hardware Reference

In-Depth Information

7

6

5

4

3

2

1

0

IDR0

ID28

ID27

ID25

ID24

ID22

ID26

ID23

ID21

IDR1

ID20

ID19

ID18

SRR(=1)

IDE(=1)

ID17

ID16

ID15

ID14

ID11

ID9

IDR2

ID13

ID12

ID10

ID8

ID7

ID4

ID3

ID2

ID1

ID0

RTR

IDR3

ID6

ID5

Figure 13.34

■

Receive/transmit message buffer extended identifier

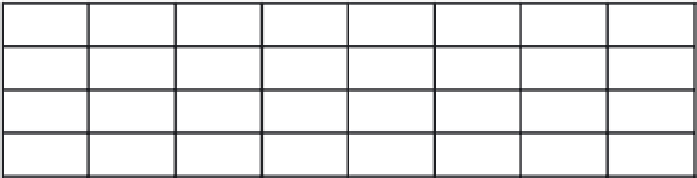

7

6

5

4

3

2

1

0

IDR0

ID10

ID9

ID8

ID7

ID6

ID5

ID4

ID3

IDR1

ID2

ID1

ID0

RTR

IDE(=0)

IDR2

IDR3

Figure 13.35

■

Receive/transmit message buffer standard identifier

The identifier consists of 29 bits (ID28,ID0) for the extended format. The ID28 bit is the

most significant bit and is transmitted first. The CAN protocol uses the identifier to arbitrate

simultaneous transmissions. The priority of an identifier is defined to be highest for the small-

est binary number. The identifier consists of 11 bits (ID10,ID0) for the standard format. The

ID10 bit is the most significant bit and is transmitted first. Similar to the extended identifier,

the priority of a standard identifier is defined to be highest for the smallest binary number.

The SRR bit is used only in the extended format and must be set to 1. The IDE bit is used

to indicate whether the identifier is an extended identifier. When set to 1, the identifier is used

as an extended identifier.

The RTR bit is used to solicit transmission from other CAN nodes. In the case of a receive

buffer, it indicates the status of the received frame and supports the transmission of an answer-

ing frame in software.

D

ATA

S

EGMENT

R

EGISTERS

(DSR0

=

DSR7)

The eight data segment registers, each with its DB7,DB0, contain the data to be transmit-

ted or received. The number of bytes to be transmitted or received is determined by the data

length code in the corresponding DLR.

D

ATA

L

ENGTH

R

EGISTER

(DLR)

The data length register has only the lowest 4 bits implemented and is used to indicate the

number of data bytes contained in the message.

T

RANSMIT

B

UFFER

P

RIORITY

R

EGISTER

(TBPR)

This register defines the local priority of the associated message buffer. The local priority is

used for the internal prioritization process of the MSCAN and is defined to be highest for the small-

est binary number. The MSCAN implements the following internal prioritization mechanism:

•

All transmission buffers with a cleared TXEx flag (bit 2, 1, or 0 of the CAN

x

TFL register)

participate in the prioritization immediately before the SOF (start of frame) is sent.

•

The transmission buffer with the lowest local priority field wins the prioritization.

Search WWH ::

Custom Search