Hardware Reference

In-Depth Information

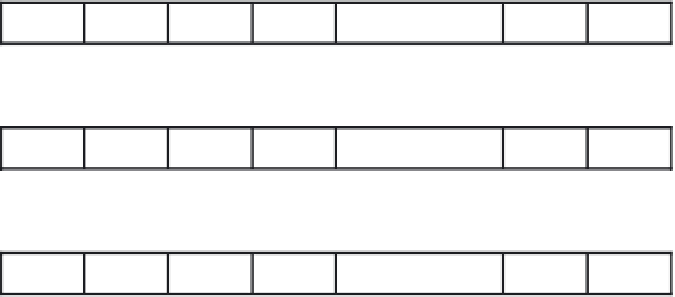

7

6

5

4

3

2

1

0

AC7

AC6

AC5

AC4

AC2

AC1

AC0

AC3

CAN

x

IDAR4

Reset:

0

0

0

0

0

0

0

0

7

6

5

4

3

2

1

0

AC7

AC6

AC5

AC4

AC3

AC2

AC1

AC0

CAN

x

IDAR5

Reset:

0

0

0

0

0

0

0

0

7

6

5

4

3

2

1

0

AC7

AC6

AC5

AC4

AC3

AC2

AC1

AC0

CAN

x

IDAR6

Reset:

0

0

0

0

0

0

0

0

7

6

5

4

3

2

1

0

AC7

AC6

AC5

AC4

AC3

AC2

AC1

AC0

CAN

x

IDAR7

Reset:

0

0

0

0

0

0

0

0

Figure 13.30

■

MSCAN identifier acceptance registers (second bank) (

x

5

0, 1, 2, 3, or 4)

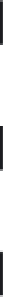

7

6

5

4

3

2

1

0

AM7

AM6

AM5

AM4

AM3

AM2

AM1

AM0

CAN

x

IDMR0

Reset:

0

0

0

0

0

0

0

0

7

6

5

4

3

2

1

0

AM7

AM6

AM5

AM4

AM3

AM2

AM1

AM0

CAN

x

IDMR1

Reset:

0

0

0

0

0

0

0

0

7

6

5

4

3

2

1

0

AM7

AM6

AM5

AM4

AM3

AM2

AM1

AM0

CAN

x

IDMR2

Reset:

0

0

0

0

0

0

0

0

7

6

5

4

3

2

1

0

CAN

x

IDMR3

AM7

AM6

AM5

AM4

AM3

AM2

AM1

AM0

Reset:

0

0

0

0

0

0

0

0

Figure 13.31

■

MSCAN identifier mask registers (first bank)

The receive message and transmit message buffers have the same outline. Each mes-

sage buffer allocates 16 bytes in the memory map containing a 13-byte data structure (from

identifier register 0 to data length register). The message buffer organization is illustrated in

Figure 13.33.

Search WWH ::

Custom Search