Hardware Reference

In-Depth Information

0

7-bit slave

address

S

R/W

A

Data

A

Data

A/A

(write)

11110XX

0

2nd byte of 10-bit

slave address

1st 7 bits of 10-bit

slave address

R

R/W

A

Data

A

Data

P

A

A/A

(write)

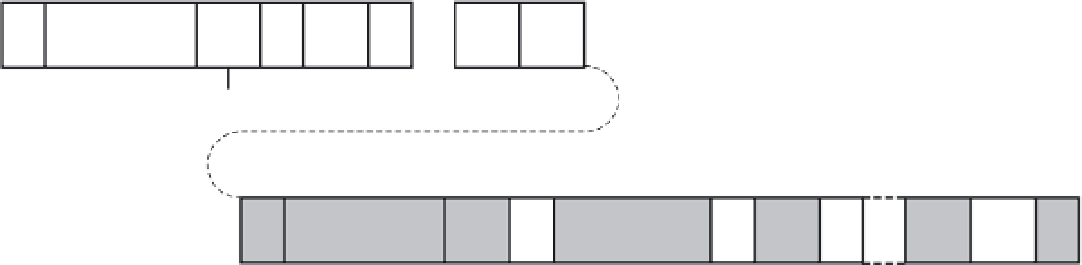

Figure 11.20

■

Combined format: A master transmits data to two slaves, one with a 7-bit address and one with

a 10-bit address

data to a second slave with a 10-bit address. The same master occupies the bus all

the time.

The I

2

C module of the HCS12 implements a subset of the I

2

C standard. It supports most of the

master and slave functions and provides interrupts on start and stop bits in hardware to determine

if a bus is free (multimaster function). Neither the 10-bit addressing nor the general call addressing

is supported by the HCS12 I

2

C module. The I

2

C module of the HCS12 may operate at baud rates of

up to 100 kbps with maximum capacitive bus loading. With a reduced bus slew rate, the device is

capable of operating at a baud rate of up to 400 kbps, provided that the I

2

C bus slew rate is less than

100 ns. The maximum communications interconnect length and the number of devices that can

be connected to the bus are limited by a maximum bus capacitance of 400 pF in all instances.

Two pins are used for data transfer.

•

Serial clock (SCL)—PJ7/SCL

•

Serial data (SDA)—PJ6/SDA

The I

2

C module works the same in normal, special, and emulation modes of the HCS12. It has

two low-power modes: wait and stop modes. The I

2

C module has fi ve registers to support its

operation.

•

I

2

C control register (IBCR)

•

I

2

C status register (IBSR)

•

I

2

C data I/O register (IBDR)

•

I

2

C frequency divider register (IBFD)

•

I

2

C address register (IBAD)

The block diagram of the I

2

C module is shown in Figure 11.21.

Search WWH ::

Custom Search