Hardware Reference

In-Depth Information

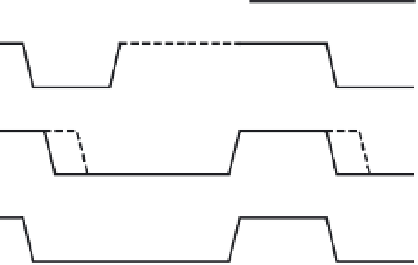

Start counting

high period

Wait

state

CLK1

Counter

reset

CLK2

SCL

Figure 11.8

■

Clock synchronization during the

arbitration procedure

When all devices concerned have counted off their low period, the clock line will be released

and go high. There will then be no difference between the device clocks and the state of the

SCL line, and all the devices will start counting their high periods. In this way, a synchronized

SCL clock is generated with its low period determined by the device with the longest clock low

period and its high period determined by the one with the shortest clock high period.

Clock synchronization occurs when multiple masters attempt to drive the I

2

C bus and be-

fore the arbitration scheme can decide which master is the winner. The I

2

C bus arbitration

process will be discussed in the next section.

H

ANDSHAKING

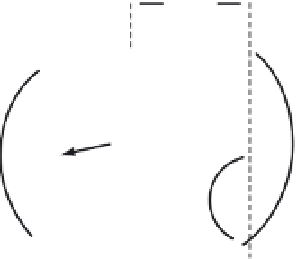

The clock synchronization mechanism can be used as a handshake in data transfer. Slave de-

vices may hold the SCL low after completion of a 1-byte transfer (9 bits). In such a case, the slave

halts the bus clock low and forces the master clock into wait states until it releases the SCL line.

C

LOCK

S

TRETCHING

The clock synchronization mechanism can be used by slaves to slow down the bit rate of

a transfer. After the master has driven SCL low, the slave can drive SCL low for the required

period and then release it. If the slave SCL low period is greater than the master SCL low period,

then the resulting SCL bus signal low period is stretched.

I

2

C allows multiple master devices to coexist in the system. In the event that two or more

master devices attempt to begin a transfer at the same time, an arbitration scheme is employed

to force one or more masters to give up the bus. The master devices continue transmitting until

one attempts a high while the other transmits a low. Since the bus driver has open drain, the bus

will be pulled low. The master attempting to transfer a high signal will detect a low on the SDA

line and give up the bus by switching off its data output stage. The winning master continues its

transmission without interruption; the losing master becomes a slave and receives the rest of the

transfer. This arbitration scheme is nondestructive: One device always wins, and no data is lost.

An example of the arbitration procedure is shown in Figure 11.9, where Data1 and Data2 are

data driven by device 1 and device 2 and SDA is the resultant data on the SDA line. The moment

there is a difference between the internal data level of the master generating Data1 and the ac-

tual level on the SDA line, its data output is switched off; this means that a high output level is

then connected to the bus. This will not affect the data transfer initiated by the winning master.

Search WWH ::

Custom Search