Hardware Reference

In-Depth Information

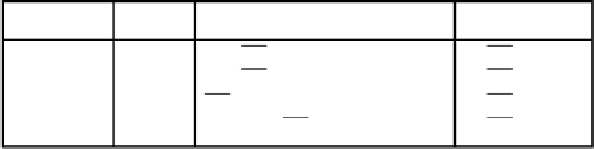

MODFEN

SSOE

Master Mode

Slave Mode

0

0

1

1

0

1

0

1

SS not used by SPI

SS not used by SPI

SS input with MODF feature

SS output

SS input

SS input

SS input

SS input

Table 10.1

■

SS input/output selection

7

6

5

4

3

2

1

0

Reset value

= 0x08

0

0

0

MODFEN BIDIROE

0

SPSWAI

SPC0

MODFEN: mode fault enable bit

0 = disable the MODF error.

1 = enable setting the MODF error.

BIDIROE: output enable in the bidirectional mode of operation

0 = output buffer disabled.

1 = output buffer enabled.

SPSWAI: SPI stop in wait mode

0 = SPI clock operates normally in stop mode.

1 = stop SPI clock generation in wait mode.

SPC0: serial pin control bit 0

With the MSTR bit in the SPI

x

CR1 register, this bit enables bidirectional pin

configuration, as shown in Table 10.2.

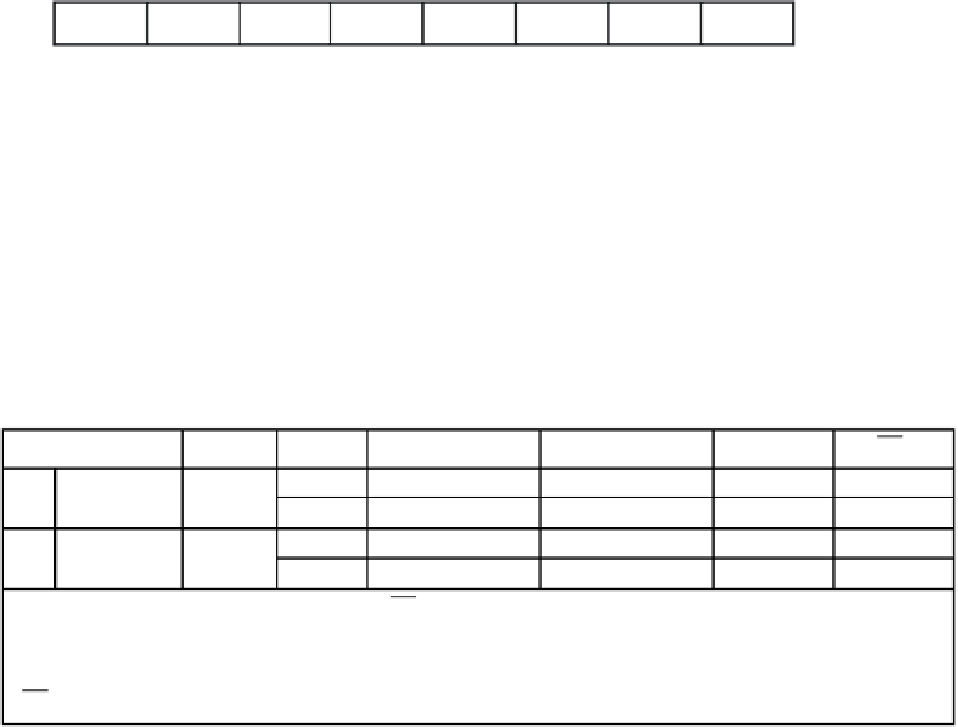

Figure 10.2

■

SPI control register 2 (SPI

x

CR2,

x

5

0, 1, or 2)

MISO

1

MOSI

2

SCK

3

SS

4

Pin Mode

SPC0

MSTR

A

B

0

0

Slave out

Slave in

SCK in

SS in

Normal

1

Master in

Master out

SCK out

SS I/O

C

D

1

0

Slave I/O

—

SCK in

SS in

Bidirectional

1

—

Master I/O

SCK out

SS I/O

1

Slave output is enabled if BIDIROE bit = 1, SS = 0, and MSTR = 0 (C).

2

Master output is enabled if BIDIROE bit = 1 and MSTR = 1 (D).

3

SCK output is enabled if MSTR = 1 (B,D).

4

SS output is enabled if MODFEN = 1, SSOE = 1, and MSTR = 1 (B,D).

Table 10.2

■

Bidirectional pin configurations

transfer data with the least significant bit first. Bit 0 (LSBF) of the SPI

x

CR1 register allows the

user to have this flexibility.

The SPI data shift rate (also called

baud rate

) is programmable. The baud rate is set by

programming the SPI

x

BR register to appropriate values. The contents of the SPI

x

BR register are

shown in Figure 10.3. The method for computing the baud rate is also given in Figure 10.3.

Search WWH ::

Custom Search