Hardware Reference

In-Depth Information

these instructions to service the interrupt request. These instructions will resume at the point

when they were interrupted.

Before the HCS12 starts to service an interrupt, it will set the I mask to disable other mask-

able interrupts. When the CPU begins to service an interrupt, the instruction queue is refilled,

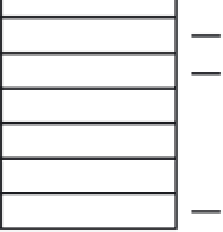

a return address is calculated, and then the return address and the contents of all CPU registers

(except SP) are saved in the stack in the order shown in Figure 6.3.

[CCR]

[A]

[B]

[X]

[Y]

SP

SP + 1

SP + 2

SP + 3

SP + 5

Return address

SP + 7

Figure 6.3

■

Stack order on entry to interrupts

T

HE

RTI I

NSTRUCTION

RTI is used to terminate interrupt service routines. RTI is an 8-cycle instruction when no

other interrupt is pending and an 11-cycle instruction when another interrupt is pending. In

either case, the first 5 cycles are used to restore the CCR, B:A, X, Y, and return address from the

stack. The HCS12 then clears the I mask to enable further maskable interrupts.

If no other interrupt is pending at this point, three program words are fetched to refill

the instruction queue from the area of the return address, and processing proceeds from there.

If another interrupt is pending after registers are restored, a new vector is fetched, and the

stack pointer is adjusted to point at the CCR value that was just recovered (SP 5 SP - 9).

This makes it appear that the registers have been stacked again. After the SP is adjusted,

three program words are fetched to refill the instruction queue, starting at the address the

vector points to. Processing then continues with execution of the instruction that is now at

the head of the queue.

There are three interrupts in this category: XIRQ pin (multiplexed with the PE0 pin), swi

instruction, and unimplemented opcode trap.

XIRQ P

IN

I

NTERRUPT

The XIRQ pin interrupt is disabled during a system reset and on entering the interrupt ser-

vice routine for an XIRQ interrupt.

During reset, both the I and X bits in the CCR register are set. This disables maskable inter-

rupts and interrupt requests made by asserting the XIRQ pin (pulled to low). After minimum

system initialization, software can clear the X bit using an instruction such as andcc #$BF.

Software cannot reset the X bit from 0 to 1 once it has been cleared, and hence the interrupt

requests made via the XIRQ pin become nonmaskable.

Search WWH ::

Custom Search