Hardware Reference

In-Depth Information

for the convenience of setting up the whole interrupt-vector table. To raise a maskable inter-

rupt source to the highest priority, simply write the low byte of the vector address of this inter-

rupt to the HPRIO register. For example, to raise the capture timer channel 7 interrupt to the

highest priority, write the value of $E0 to the HPRIO register.

All HCS12 reset and interrupt vectors are stored in a table (shown in Table 6.1) located at

$FF8C to $FFFF. In Table 6.1, exceptions that have higher vector addresses are at higher priori-

ties. Not all the exceptions are available in all HCS12 members.

IRQ P

IN

I

NTERRUPT

The IRQ pin (multiplexed with the PE1 pin) is the only external maskable interrupt signal.

The IRQ pin interrupt can be edge triggered or level triggered. The triggering method is selected

by programming the IRQE bit of the Interrupt Control Register (IRQCR). The IRQ pin interrupt

has a local enable bit IRQEN bit, which is bit 6 of the IRQCR. The contents of the IRQCR reg-

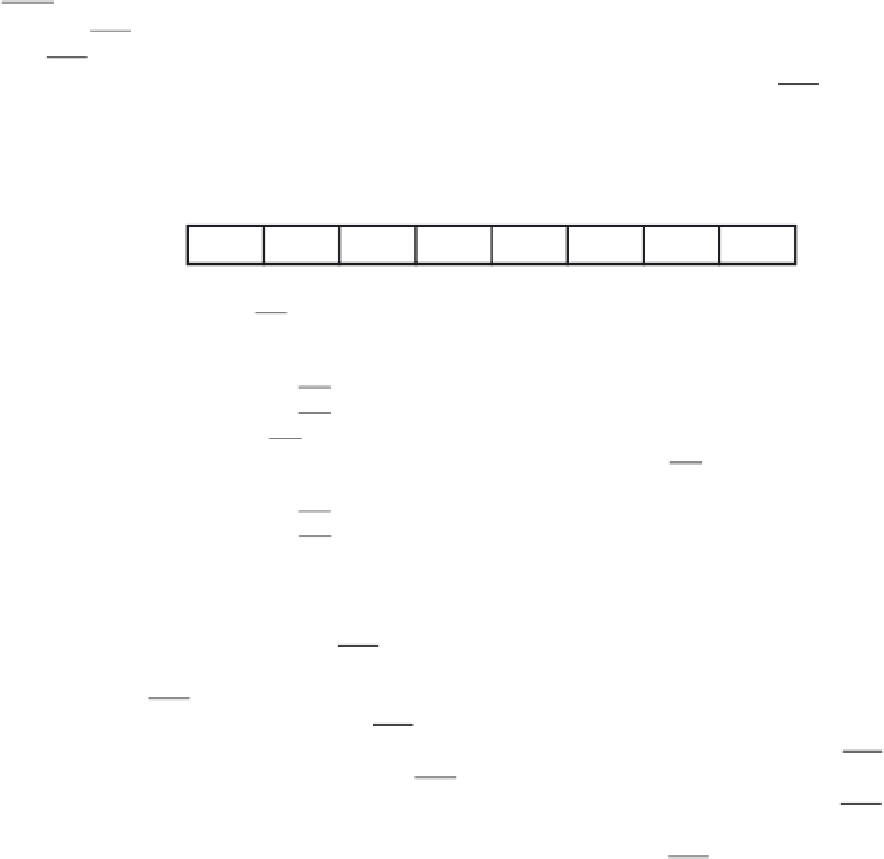

ister are shown in Figure 6.2.

7

6

5

4

3

2

1

0

0

IRQE

IRQEN

0

0

0

0

0

Reset:

0

1

0

0

0

0

0

0

IRQE: IRQ edge-sensitive only bit

IRQE can be written once in normal mode. In special modes, it can be

written any time, but the first write is ignored.

1 = IRQ pin responds only to falling edge

0 = IRQ pin responds to low level

IRQEN: IRQ enable bit

IRQEN bit can be written any time in all modes. The IRQ pin has an

internal pull-up.

1 = IRQ pin interrupt enabled

0 = IRQ pin interrupt disabled

Figure 6.2

■

Interrupt control register (IRQCR)

The advantage of making the IRQ interrupt

level sensitive

(active low) is that it allows mul-

tiple external interrupt sources to be tied to this pin. Whenever one of the interrupt sources (that

are tied to the IRQ pin) is low, an interrupt request will be detected by the HCS12. The user of

this method must make sure that the IRQ signal is de-asserted (goes high) before the HCS12 exits

the interrupt service routine if there are no other pending interrupts connected to the IRQ pin.

The major advantage of making the IRQ interrupt

edge sensitive

(falling edge) is that the

user does not need to be concerned about the duration of the assertion time of the IRQ signal.

However, this approach is not appropriate for a noisy environment. In a noisy environment, any

noise spike could generate an undesirable interrupt request on the IRQ pin.

I

NTERRUPT

R

ECOGNITION

Once enabled, an interrupt request can be recognized at any time after the I mask bit is

cleared. When an interrupt service request is recognized, the CPU responds at the completion

of the instruction being executed. Interrupt latency varies according to the number of cycles

required to complete the current instruction. The HCS12 has implemented a few instructions to

support fuzzy-logic rule evaluation. These instructions, which take a much longer time to com-

plete, include fuzzy-logic rule evaluation (REV), fuzzy-logic rule evaluation weighted (REVW),

and weighted-average (WAV) instructions. The HCS12 does not wait until the completion of

Search WWH ::

Custom Search