Hardware Reference

In-Depth Information

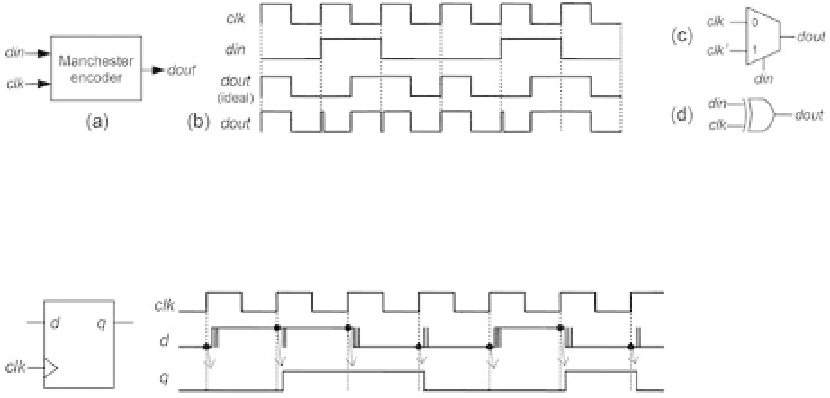

Figure 2.13

A circuit (Manchester encoder) in which multiple inputs can change at the same time, subjecting

the output to glitches that cannot be prevented with a combinational circuit.

Figure 2.14

Glitch elimination with a l ip-l op.

The problem with the solution above is that it covers only transitions in which just

one input value changes. Because in actual designs multiple inputs can change

(approximately) at the same time, this approach is of little practical interest.

An example in which more than one input can change is depicted in

i gure 2.13,

which consists of a Manchester encoder. Figure 2.13a shows the circuit ports, and

i gure 2.13b shows the waveform that must be produced at the output (

dout

must be

a '1'-to-'0' pulse when

din

= '0' or a '0'-to-'1' pulse if

din

= '1'). Looking at the wave-

forms, we verify that

dout

=

clk

when

din

= '0' or

dout

=

clk

when

din

= '1', so this

encoder can be implemented with a simple multiplexer, as depicted in

′

i gure 2.13c.

Observe, however, in i gure 2.13b, that

clk

and

din

can change at the same time, so

uni xable glitches are potentially expected. Indeed, the last plot for

dout

in i gure 2.13b

takes into account such a possibility (due to different propagation delays), resulting

in a series of glitches. Just for completeness, note that the trivial multiplexer of i gure

2.13c, having the equation

dout

=

clk

⋅

din

′ +

clk

din

, can be implemented using just an

XOR gate for

din

and

clk

, as shown in i gure 2.13d.

If the combinational circuit is part of a synchronous system (as in state machines),

then there is a simple—and, more importantly, systematic and guaranteed—solution

for glitch elimination, which consists of passing the noisy signal through a DFF.

Because glitches in a synchronous signal can only appear right after a clock edge, when

such a signal is passed through a DFF the resulting output will be automatically free

from glitches. This procedure is illustrated in i gure 2.14, where

d

(synchronous) has

glitches but

q

has not. Note that there is a price to pay, however, which is one clock

cycle (if the same clock edge that produces

d

is used in the DFF) or one-half of a clock

cycle (if the opposite clock edge is employed) of delay with respect to the original

′

⋅