Hardware Reference

In-Depth Information

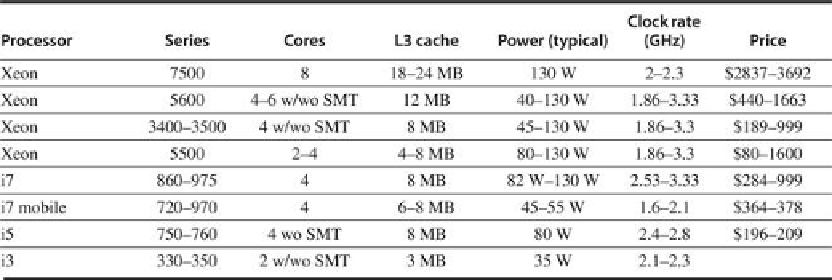

FIGURE 5.34

The characteristics for a range of Intel parts based on the Nehalem mi-

croarchitecture

. This chart still collapses a variety of entries in each row (from 2 to 8!). The

price is for an order of 1000 units.

In the 1980s and 1990s, with the birth and development of ILP, software in the form of op-

timizing compilers that could exploit ILP was key to its success. Similarly, the successful ex-

ploitation of thread-level parallelism will depend as much on the development of suitable soft-

ware systems as it will on the contributions of computer architects. Given the slow progress

on parallel software in the past 30-plus years, it is likely that exploiting thread-level parallel-

ism broadly will remain challenging for years to come. Furthermore, your authors believe that

there is signiicant opportunity for beter multicore architectures. To design those architects

will require a quantitative design discipline and the ability to accurately model tens to hun-

dreds of cores running trillions of instructions, including large-scale applications and oper-

ating systems. Without such a methodology and capability, architects will be shooting in the

dark. Sometimes you're lucky, but often you miss.

5.11 Historical Perspectives and References

Section L.7 (available online) looks at the history of multiprocessors and parallel processing.

Divided by both time period and architecture, the section features discussions on early experi-

mental multiprocessors and some of the great debates in parallel processing. Recent advances

are also covered. References for further reading are included.

Case Studies and Exercises by Amr Zaky and David

A. Wood

Case Study 1: Single-Chip Multicore Multiprocessor

Concepts illustrated by this Case Study

■ Snooping Coherence Protocol Transitions

■ Coherence Protocol Performance

■ Coherence Protocol Optimizations

■ Synchronization

Search WWH ::

Custom Search