Hardware Reference

In-Depth Information

■ Memory Consistency Models Performance

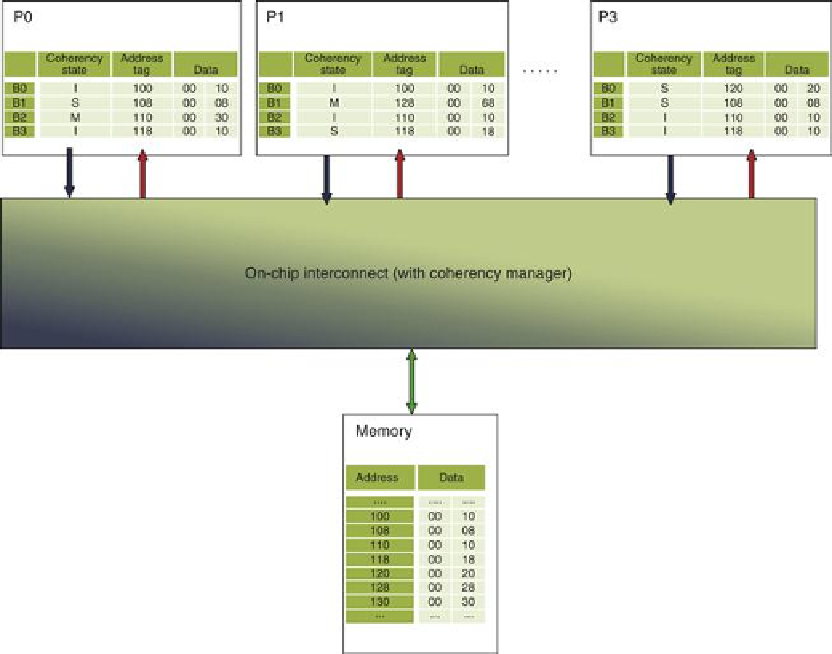

The simple, multicore multiprocessor illustrated in

Figure 5.35

represents a commonly im-

plemented symmetric shared-memory architecture. Each processor has a single, private cache

with coherence maintained using the snooping coherence protocol of

Figure 5.7

. Each cache

is direct-mapped, with four blocks each holding two words. To simplify the illustration, the

cache-address tag contains the full address, and each word shows only two hex characters,

with the least significant word on the right. The coherence states are denoted M, S, and I

(Modiied, Shared, and Invalid).

FIGURE 5.35

Multicore (point-to-point) multiprocessor

.

5.1 [10/10/10/10/10/10/10] <5.2> For each part of this exercise, assume the initial cache and

memory state as illustrated in

Figure 5.35

. Each part of this exercise specifies a sequence of

one or more CPU operations of the form:

P#: <op> <address> [<value>]

where

P#

designates the CPU (e.g.,

P0

),

<op>

is the CPU operation (e.g., read or write),

<ad-

dress>

denotes the memory address, and

<value>

indicates the new word to be assigned on

a write operation. Treat each action below as independently applied to the initial state as

Search WWH ::

Custom Search