Hardware Reference

In-Depth Information

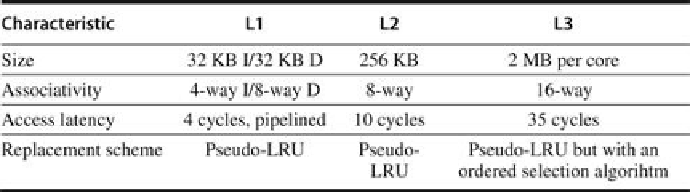

FIGURE 2.20

Characteristics of the three-level cache hierarchy in the i7

. All three

caches use write-back and a block size of 64 bytes. The L1 and L2 caches are separate for

each core, while the L3 cache is shared among the cores on a chip and is a total of 2 MB per

core. All three caches are nonblocking and allow multiple outstanding writes. A merging write

buffer is used for the L1 cache, which holds data in the event that the line is not present in L1

when it is written. (That is, an L1 write miss does not cause the line to be allocated.) L3 is in-

clusive of L1 and L2; we explore this property in further detail when we explain multiprocessor

caches. Replacement is by a variant on pseudo-LRU; in the case of L3 the block replaced is

always the lowest numbered way whose access bit is turned off. This is not quite random but

is easy to compute.

Search WWH ::

Custom Search