Image Processing Reference

In-Depth Information

The read pulse is also applied to the portion just above the readout pass of the electrode

ϕV1, which also increases the potential of the charge readout path. Thus, the readout path

is efficiently increased by the synergetic effect

6

from both the VCCD channel and surface

sides, and signal charges integrated in the PD are read out to the VCCD channel. The read-

out signal charge packets are transferred in the VCCD channel by applied clock pulses of

[M, L] of ϕ1 and ϕ3 and [H, L] of ϕ2 and ϕ4. Then, signal charge packets corresponding to

one-line pixels are transferred to the HCCD and each charge packet is transferred through

the HCCD to the output amplifier to be converted to signal voltage output, as shown in

Figure 5.9. Once the first field readout is completed, the second field readout starts by

applying a read pulse of ϕ3 to electrode ϕV3 and is carried out in the same manner as the

first field readout. The readouts of these two fields are repeated in alternate shifts. In this

mode, odd-line pixel signals are output in the first field readout period, while even lines

are output in the second field readout period.

This is a kind of interlaced mode called frame integration mode. It is a typical driving

mode for still image capture, with many more field numbers in the current era.

If this mode is applied for moving pictures, a phenomenon named

system lag

occurs, as

shown in Figure 5.12a. The sensor has 500 line pixels, that is, 1000 transfer gate electrodes

for a four-phase VCCD, and can treat 250 signal charge packets in a one-column VCCD.

The first field signal of odd-line pixels and second field signal of even-line pixels, each of

250 lines, are output alternately in 1/60 s. Although the integration period is 1/30 s, images

are output every 1/60 s. There is a 50% overlap in the time domain between consecutive

fields, as shown in Figure 5.12a; that is, the images with time information 50% the same are

successively displayed. This causes an image lag phenomenon known as system lag. Also,

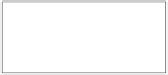

there is a driving mode called field integration mode, as shown in Figure 5.12b. In this

mode, signal charges of all pixels are read out to the VCCD and signal charges of adjacent

(a)

250 lines

1/30 s (integration period)

is half of the

signal has the same

information

as the next field

500 lines

1st (odd)

Overlap of

time information:

+

50%

2nd (even)

System lag (50%)

1/60 s

Output/display

Low resolution of

moving objects

(b)

250 lines

1/60 s (integration period)

+

+

+

+

500 lines

1st (odd+even)

Overlap of

time information:

is signal is

independent from

the next field

+

+

+

0%

+

+

+

+

2nd (even+odd)

Alternating pixel charge addition of adjacent lines

No system lag

1/60 s

Output/display

Key: CFA solution that enables alternative pixel charge addition

FIGURE 5.12

(a,b) Comparison of integration modes for moving pictures.