Image Processing Reference

In-Depth Information

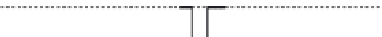

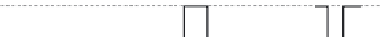

φV4

φ

φV1

SiO

2

Si

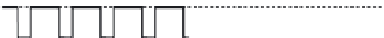

FIGURE 5.10

Pixel structure of an IT-CCD.

voltage clocks having [H, M, L] (about 12, 0, and ‒5 V, respectively) ϕ1 and ϕ3 are applied

to electrodes ϕV1 and ϕV3, and two-value voltage clocks having [H, L] (about 0 and ‐5V) ϕ2

and ϕ4 are applied to ϕV2 and ϕV4, respectively.

By applying a read pulse of ϕ1 to electrode ϕV1, the VCCD channel potential under

electrode ϕV1 in Figure 5.10, which is already depleted as in Figure 5.6b, rises, as shown in

Figure 5.6c, and the VCCD channel depletion region is enlarged to the charge readout path.

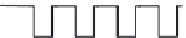

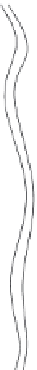

First field output period

Second field output period

Read pulse

H

M

VCCD

transfer pulse

φ1

L

VCCD

transfer pulse

H

φ2

L

Read pulse

H

M

VCCD

transfer pulse

φ3

L

H

VCCD

transfer pulse

φ4

L

Time

FIGURE 5.11

Readout and transfer clock of a four-phase CCD in interlace mode.