Information Technology Reference

In-Depth Information

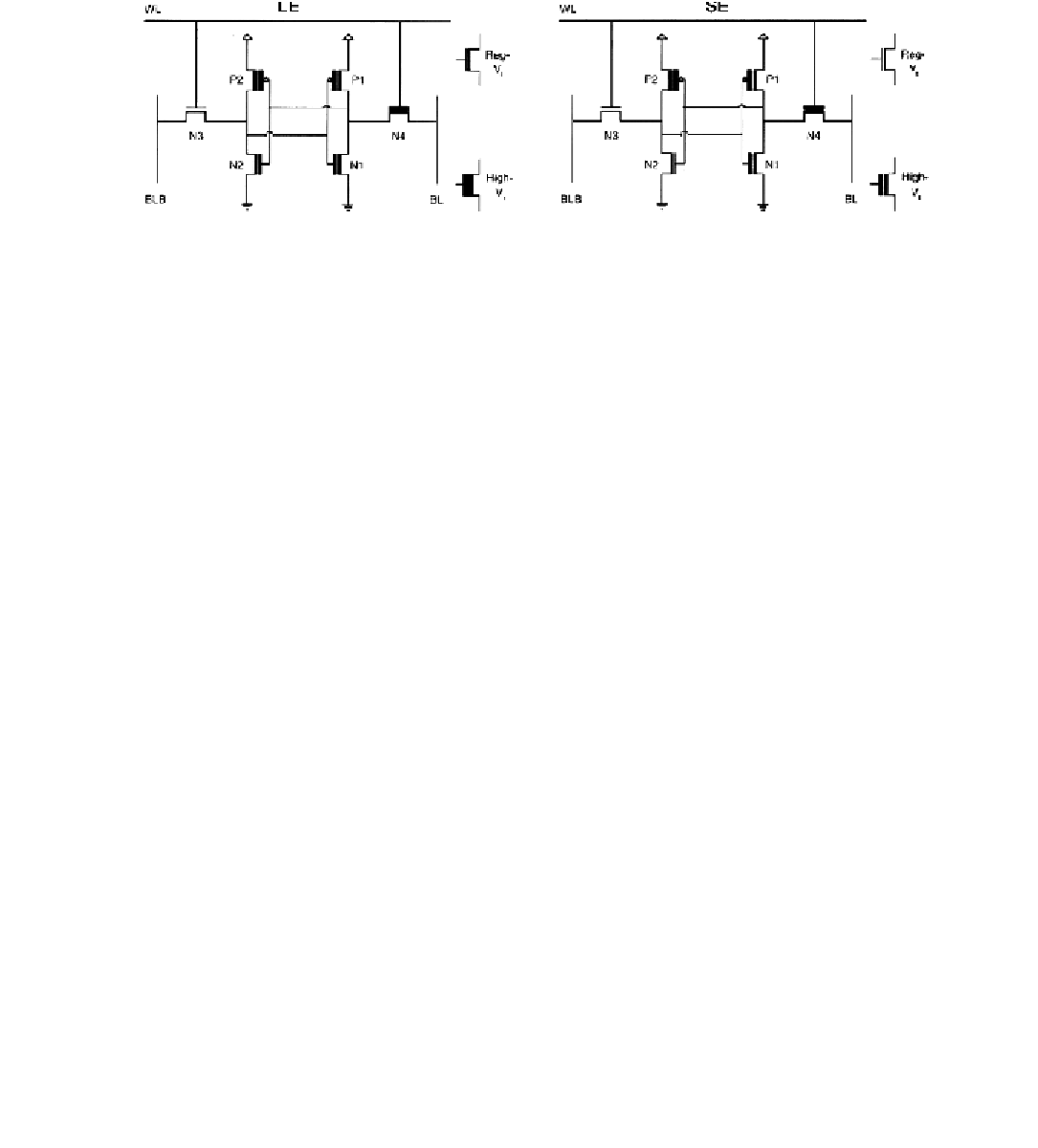

FIGURE 5.24:

Two improved Asymmetric Cells: the Leakage Enhanced (LE) and Speed Enhanced

(SE). Reproduced from [

18

]. Copyright 2003 IEEE.

connected on extra dummy cells, Azizi et al. are able to exploit the timing asymmetry in the

discharge of the bitlines and trick the sense-amp in detecting zeros almost as fast as detecting

ones. The details are explained in [

17

,

18

].

The asymmetric design in Figure 5.23 is only one of the nine plausible asymmetric

designs—but not the best. Azizi et al. describe and evaluate the other nine designs and determine

for each the leakage savings when storing a zero or a one and the respective latencies in the

discharge of the bitlines BL and BLB [

18

].

Two improved designs are shown in Figure 5.24. The first is a leakage enhanced (LE)

version and the second is a speed enhanced (SE) version. In the LE cell, the replacement of

N1 and P2 by high-

V

T

devices improves the leakage power consumption when the cell holds

a 1. The savings are 40% and 7% for holding a 0 or a 1 respectively. The discharge of the

BLB is slowed further, reaching 61% of the normal low-

V

T

cell but the discharge of the BL

is not affected remaining 12% slower than the normal cell. Still the extra latency for the BLB

is hidden by the new sense-amp design that detects a zero from the dummy bitlines exactly

because the BLB discharge is slowed. The SE design puts the emphasis on speed. Although

its leakage reduction is not as impressive (only 2

compared to a normal cell when

holding a 0 and a 1 respectively), its response time, with the help of the new sense-amp, is

virtually identical to a normal (low-

V

T

) cell.

×

and 7

×

Search WWH ::

Custom Search