Information Technology Reference

In-Depth Information

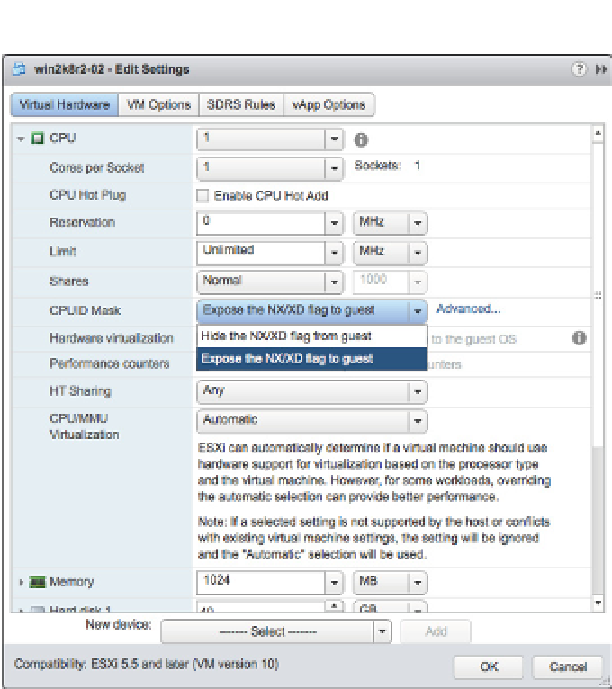

Figure 12.9

h e option for

masking the NX/

XD bit is controlled

on a per-VM basis.

For features other than the NX/XD bit, you would have to delve into custom CPU masks.

This is where you will step outside the bounds of VMware support. Looking at the dialog box

in Figure 12.9, you'll note the Advanced button. Clicking the Advanced button opens the CPU

Identii cation Mask dialog box, shown in Figure 12.10.

In this dialog box, you can create custom CPU masks to mark off specii c bits within the CPU

ID value. We won't go into great detail here because all of this is unsupported by VMware, and

it's generally not needed provided you run hardware that is on the HCL. However, Scott Lowe

has two blog articles that provide additional information:

Fortunately, there's an easier—and fully supported—way of handling this issue, and it's

called VMware Enhanced vMotion Compatibility (EVC).

Using VMware Enhanced vMotion Compatibility

Recognizing that potential compatibility issues with vMotion could be a signii cant problem,

VMware worked closely with both Intel and AMD to craft functionality that would address this

issue. On the hardware side, Intel and AMD put functions in their CPUs that would allow them

to modify the CPU ID value returned by the CPUs. Intel calls this functionality FlexMigration;

AMD simply embedded this functionality into its existing AMD-V virtualization extensions.