Information Technology Reference

In-Depth Information

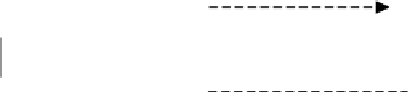

(point 1 in the figure) until it sees a data-accept signal. When the slave sees a data-

ready signal, it will assert the data-accept line (point 2 in the figure). The rising of the

data-accept line will trigger the falling of the data-ready line and the removal of data

from the bus. The falling of the data-ready line (point 3 in the figure) will trigger the

falling of the data-accept line (point 4 in the figure). This handshaking, which is

called fully interlocked, is repeated until the data is completely transferred. Asyn-

chronous bus is appropriate for different speed devices.

8.5.3. Bus Arbitration

Bus arbitration is needed to resolve conflicts when two or more devices want to

become the bus master at the same time. In short, arbitration is the process of select-

ing the next bus master from among multiple candidates. Conflicts can be resolved

based on fairness or priority in a centralized or distributed mechanisms.

Centralized Arbitration

In centralized arbitration schemes, a single arbiter is

used to select the next master. A simple form of centralized arbitration uses a bus

request line, a bus grant line, and a bus busy line. Each of these lines is shared by

potential masters, which are daisy-chained in a cascade. Figure 8.12 shows this

simple centralized arbitration scheme.

In the figure, each of the potential masters can submit a bus request at any time.

A fixed priority is set among the masters from left to right. When a bus request is

received at the central bus arbiter, it issues a bus grant by asserting the bus grant

line. When the potential master that is closest to the arbiter (potential master 1) sees

the bus grant signal, it checks to see if it had made a bus request. If yes, it takes over

the bus and stops propagation of the bus grant signal any further. If it has not made a

request, it will simple turn the bus grant signal to the next master to the right (potential

master 2), and so on. When the transaction is complete, the busy line is deasserted.

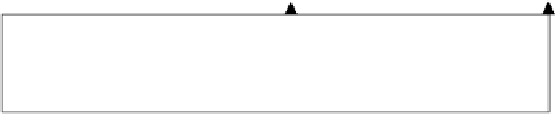

Instead of using shared request and grant lines, multiple bus request and bus grant

lines can be used. In one scheme, each master will have its own independent request

and grant line as shown in Figure 8.13. The central arbiter can employ any priority-

based or fairness-based tiebreaker. Another scheme allows the masters to have mul-

tiple priority levels. For each priority level, there is a bus request and a bus grant

line. Within each priority level, daisy chain is used. In this scheme, each device is

attached to the daisy chain of one priority level. If the arbiter receives multiple

Bus Grant

Potential

Master 1

Potential

Master 2

Potential

Master n

Central

Bus

Arbiter

Bus Request

Bus Busy

Figure 8.12 Centralized arbiter in a daisy-chain scheme

Search WWH ::

Custom Search