Information Technology Reference

In-Depth Information

t

0

In-bus

R

0

Inst-x

R

0

in-bus

Add

ALU

R

2

out-bus1

R

2

out-bus2

R

2

R

1

Out-bus 1

Out-bus 2

Figure 5.8 Signals generated to execute Inst-x on three-bus datapath during time period t

0

(R

0

in-bus), and (Add) will select R

1

as a source on out-bus1, R

2

as a source on out-

bus2, R

0

as destination on in-bus, and select the ALUs add function, respectively.

Example 2

Let us repeat the operation in the previous example using the one-bus

datapath shown in Fig. 5.3. We have shown earlier that this operation can be carried

out in three steps using the one-bus datapath. Suppose that the op-code field of the

current instruction was decoded to Inst-x type. The following table shows the needed

steps and the control sequence.

Step

Instruction type

Micro-operation

t

0

Inst-x

A

(R

1

)

Select R

1

as source (R

1

out)

Select A as destination (A in)

t

1

Inst-x

B

(R

2

)

Select R

2

as source (R

2

out)

Select B as destination (B in)

t

2

Inst-x

R

0

(A)

þ

(B)

Select the ALU function Add (Add)

Select R

0

as destination (R

0

in)

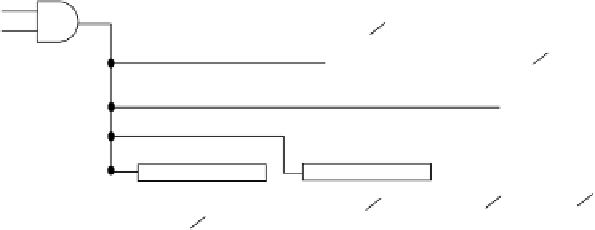

Figure 5.9 shows the signals generated to execute Inst-x during time periods t

0

,

t

1

, and t

2

. The AND gates ensure that the appropriate signals will be issued when the

op-code is decoded into Inst-x and during the appropriate time period. During t

0

, the

signals (R

1

out) and (A in) will be issued to move the contents of R

1

into A. Similarly

during t

1

, the signals (R

2

out) and (B in) will be issued to move the contents of R

2

into B. Finally, the signals (R

0

in) and (Add) will be issued during t

2

to add the con-

tents of A and B and move the results into R

0

.

5.5.1. Hardwired Implementation

In hardwired control, a direct implementation is accomplished using logic cir-

cuits. For each control line, one must find the Boolean expression in terms of the

input to the control signal generator as shown in Figure 5.7. Let us explain the

Search WWH ::

Custom Search