Information Technology Reference

In-Depth Information

3

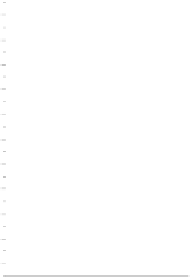

Simulation Results

1.6

1x10

6

DM-DGS

DMG

SMG

DM-DGS

DMG

SMG

9x10

5

1.4

8x10

5

7x10

5

1.2

6x10

5

1.0

5x10

5

4x10

5

0.8

3x10

5

2x10

5

0.6

1x10

5

M

L1

M

L2

0

0.4

0.00

0.02

0.04

0.06

0.00

0.02

0.04

0.06

Along the lateral direction of the device (

μ

m)

Fig. 2.

Potential and Electric field of SMG, DMG, DM-DGS devices along the channel

direction near the silicon-oxide interface at V

DS

= 1 V for L =40 nm, T

si

=8 nm and T

ox

=2 nm

Fig. 2 shows the potential and electrical field distributions along the channel

direction near the silicon-oxide interface for a drain voltage (V

DS

)

= 1 V and gate

voltage (V

GS

) of 1 V. The potential distributions of DMG and DM-DGS DGJLT have

abrupt change at the workfunction transition point from W

M1

to W

M2

, whereas SMG

DGJLT follows a monotonous trend from source to drain. This enhances the electric

field of DMG and DM-DGS with two peaks, but for SMG DGJLT there is only one

peak near the drain. Out of the three devices mentioned, DM-DGS has lowest peak

near the drain, indicating that it suppresses SCE and hot carrier effect more

effectively. This is due to better gate control of DM-DGS on the channel region. The

electron velocity in the channel can be controlled by tailoring the first peak with

proper workfunction of the metal gates [11].

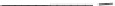

45

1.6

40

1.4

35

1.2

SMG

DM-DGS

DMG

30

DM-DGS

DMG

SMG

1.0

25

0.8

20

0.6

15

0.4

10

0.2

5

0.0

0

-0.2

0.0

0.2

0.4

0.6

0.8

1.0

Gate Voltage, V

GS

(V)

Fig. 3.

Transconductance (G

m

) and transconductance to drain current ratio (Gm/I

D

) with respect

to gate voltage for the devices at V

DS

= 1 V for L =40 nm, T

si

=8 nm and T

ox

=2 nm