Information Technology Reference

In-Depth Information

Programmable interrupt controller (PIC)

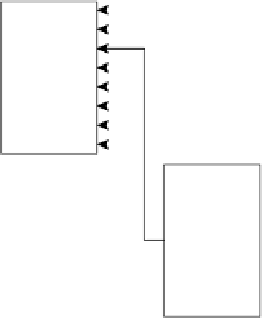

The PC uses the 8259 PIC to control hardware-generated interrupts. It is known as a pro-

grammable interrupt controller and has eight input interrupt request lines and an output line

to secondary PIC are then assigned IRQ lines of

IRQ8

to

IRQ15

. This set-up is shown in

Figure 2.13. When an interrupt occurs on any of these lines it is sensed by the processor on

interrupt the processor. Originally, PCs only had one PIC and eight IRQ lines (

IRQ0

-

IRQ7

).

Modern PCs can use up to 15 IRQ lines which are set up by connecting a secondary PIC in-

terrupt request output line to the

IRQ2

line of the primary PIC. The interrupt lines on the

IRQ2

line. The processor then interrogates the primary and secondary PIC for the interrupt

line which caused the interrupt.

The primary and secondary PICs are programmed via port addresses 20h and 21h, as

given in Table 2.7. The operation of the PIC is programmed using registers. The IRQ input

lines are either configured as level-sensitive or edge-triggered interrupt. With edge-triggered

interrupts, a change from a low to a high on the IRQ line causes the interrupt. A level-

sensitive interrupt occurs when the IRQ line is high. Most devices generate edge-triggered

interrupts.

IRQ0

IRQ1

IRQ2

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

PI

C

1

Interrupt

request

IRQ8

IRQ9

IRQ10

IRQ11

IRQ12

IRQ13

IRQ14

IRQ15

PIC 2

Figure 2.13

PC PIC connections

In the IMR an interrupt line is enabled by setting the assigned bit to a 0 (zero). This allows

the interrupt line to interrupt the processor. Figure 2.14 shows the bit definitions of the IMR.

For example, if bit 0 is set to a zero then the system timer on

IRQ0

is enabled.

Table 2.7

Interrupt port addresses

Port address

Name

Description

20h

Interrupt control register

(ICR)

Controls interrupts and signifies the end of an

interrupt

21h

Interrupt mask register

(IMR)

Used to enable and disable interrupt lines