Information Technology Reference

In-Depth Information

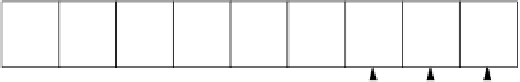

IRQ7

IRQ5

IRQ3

IRQ1

0

-

enable

1

-

disable

0

-

enable

1

-

disable

0

-

enable

1

-

disable

0

-

enable

1

-

disable

IMR (21h)

IRQ6

IRQ4

IRQ2

IRQ0

0

-

enable

1

-

disable

0

-

enable

1

-

disable

0

-

enable

1

-

disable

0

-

enable

1

-

disable

Figure 2.14

Interrupt mask register bit definitions

In the example code given next the lines

IRQ0

,

IRQ1

and

IRQ6

are allowed to interrupt the

processor, whereas,

IRQ2

,

IRQ3

,

IRQ4

and

IRQ7

are disabled:

_outp(0x21)=0xBC; /* 1011 1100 enable disk

(bit 6), keyboard (1) and timer (0) interrupts

*/

When an interrupt occurs all other interrupts are disabled and no other device can interrupt

the processor. Interrupts are enabled again by setting the EOI bit on the interrupt control port,

as shown in Figure 2.15.

The following code enables interrupts:

_outp(0x20,0x20); /* EOI command */

0

0

0

ICR (20h)

Interrupt request

level to be acted on

0

-

000

1

-

001

2

-

010

and so on.

EOI signal

1

-

end of interrupt

Figure 2.15

Interrupt control register bit definitions

2.3

Interfacing

There are two main methods of communicating with external equipment, either they are

mapped into the physical memory and given a real address on the address bus (memory

mapped I/O) or they are mapped into a special area of input/output memory (isolated I/O).