Biomedical Engineering Reference

In-Depth Information

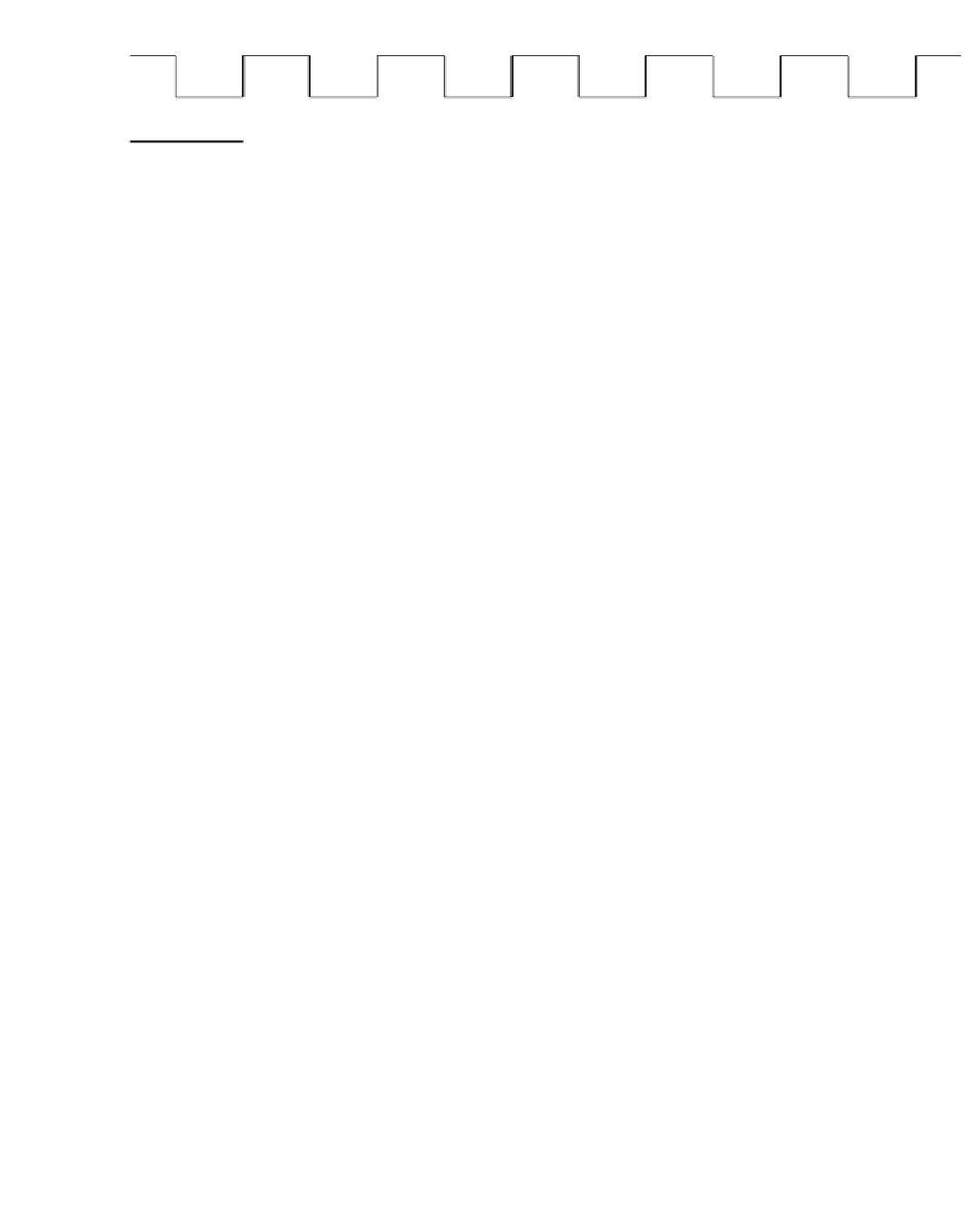

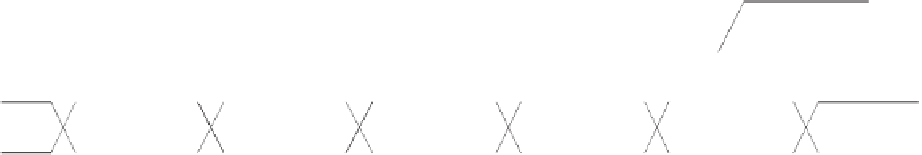

Clock

End Address+1

RAM

Address

End Address

Address 00

Address 01

Address 02

End Address-1

Reset

Data

{

D0-D30

RAM

Data @

End Address-1

Data @

End Address

Data @

Address 00

Data @

Add

ress 01

Data @

Address 02

D31

D31=1

D31=0

D31=1

Data to

DACs &

Markers

(DL0-DL30)

Data @

End Address-2

Data @

End Address-1

Data @

End Address

Data @

Address 00

Data @

Address 01

Data @

Address 02

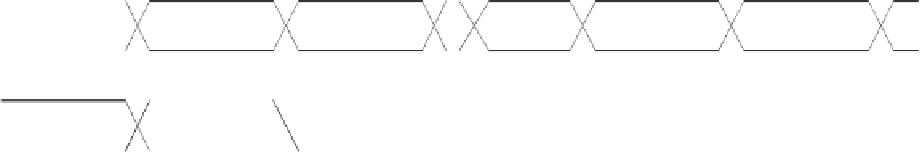

*LOC RESET

IC15 Pin 3

(*Counters Enable)

Triggered

Mode

External

Trigger

End Address+1

RAM

Address

Address 01

End Address

Address 00

Figure 6.12

Under operating conditions, the arb's control logic ensures that each sample of the waveform sequence has equal length by

presenting the data contents only on the opposite edges of the clock from those that cause address transitions. In the triggered mode, trigger

ambiguity is less than one clock cycle.

Rather than using a direct addressing scheme, very high speed arbs overcome the

RAMs' access time shortcomings by operating several RAM banks in parallel. In this mul-

tiplexed addressing scheme, one or more RAM banks are being accessed and allowed to

settle while current data are taken from a di

erent RAM. As the address is updated, data

are taken from one of the RAMs that already has valid data available. A 4 : 1 multiplexed

memory arb, for example, could use four low-cost 50-ns RAMs to achieve 80 MS/s. We

chose not to use the more complex multiplexed approach, since 20 MS/s provided us with

su

ff

flexibility for our applications in the generation of relatively low frequency sig-

nals for evaluating biomedical instruments.

Once analog signals are available at the DAC outputs, the circuit provides for their

cient

fl

o

ered for output. In addition, a summing channel is

provided to expand the arb's versatility. The local sampling clock is generated by IC33,

Maxim's MAX038 high-frequency waveform generator IC. Although this IC is typically

used as a function generator, it is used within the circuit of Figure 6.15 as an oscillator

whose frequency can be controlled over the range 20 Hz to 20 MHz. Alternatively, the

ff

seting and scaling prior to being bu

ff

Search WWH ::

Custom Search