Biomedical Engineering Reference

In-Depth Information

maximum frequency of spectral components for the arbitrary signal. Even an assembly-

language program copying the contents of sequential addresses on RAM to an I/O location

would result in DAC writing rates of a few megapoints per second at the most.

Instead of having a DAC interfaced to memory through a microprocessor, arbs have ded-

icated RAM that is interfaced directly to the DAC. In this way, update rates are limited only

by the access time of the RAM and by the speed of the DAC. As such, commercial arbs can

currently be purchased with maximum writing rates in the vicinity of 1 gigapoint/s, yielding

bandwidths of up to 500 MHz.

Direct Digital Synthesis

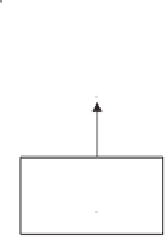

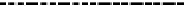

A generator capable of directly synthesizing an analog signal from digital data has at its

core a memory that contains the full time-domain digital representation of the waveform

desired. To generate the analog signal, the discretized point-by-point version of the wave-

form is played in a sequential manner through the generator's DAC. A simple form of such

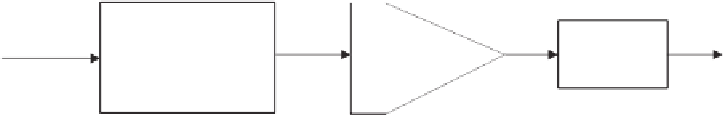

generator is a direct digital synthesizer (DDS). As shown in Figure 6.7, an address gener-

ator circuit controls the way in which samples stored in ROM are delivered to the DAC's

input. On each clock pulse delivered to the address generator, a new address is issued to

the ROM such that data for the next point in the sequence are presented to the DAC.

The ROM in a DDS generator most often contains data for generation of a complete

single cycle of a sinusoidal waveform. The address generator is a simple counter, and the

addresses it generates constitute the various phase angles

φ

for which samples of the sine

wave sin

are available in ROM. The series of values coming out of this ROM lookup

table as a function of incrementing phase angles is translated into an analog sine wave by

a D/A converter (DAC).

Obviously, if the clock presented to the phase accumulator counter remains constant,

the rate at which phases are generated remains constant, and the end result is a sine wave

φ

Phase Accumulator

V

out

t

n bits

Counter

Low-Pass

Filter

RO

M

DAC

Output

Sine Look-up Table

Phase

Increment

Register

Address

Generator

Ci

rcu

i

t

Figure 6.7

In a direct digital synthesizer (DDS), an address generator circuit or phase accumulator controls the way in which samples

stored in a ROM lookup table are delivered to the DAC's input. Control over the output frequency is achieved by selecting an appropriate

phase accumulator increment.

Search WWH ::

Custom Search