Cryptography Reference

In-Depth Information

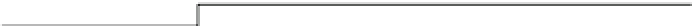

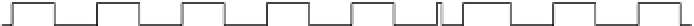

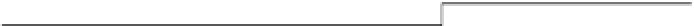

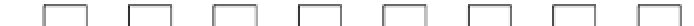

CLK_A

CLK_B

EXEC

Trigger_out

1. Trigger with set constant delay by the oscilloscope and output Triggered Signal

2.Wait for constant clock edges

Selector

3.Change CLK source with set delay by the glitch controller

CLK

Tg

Time

Fig. 18.4

Schematic for generating a clock glitch

CLK_A and CLK_B. In these experiments, we set both CLK_A and CLK_B to

24 MHz (a period of approximately 41

.

7 ns). At the start of the calculation, the

following steps are performed.

1. The oscilloscope detects the positive edge of the EXEC signal, and outputs the

Trigger_out signal with a constant delay that we set. The timing of the Trigger_out

signal output does not need to be synchronized with CLK_A or CLK_B. Then,

the glitch controller module detects it. We can set any length of delay using the

delay function of the oscilloscope.

2. After detecting the Trigger_out signal, the glitch controller module waits for

constant clock edges, which we set.

3. Then, the glitch controller module changes the CLK source from CLK_A to

CLK_B with a short constant delay, which we set.

In this example, the glitch controller module waits for three constant positive clock

edges, and then causes the next CLK positive edge to rise at a different time. One

clock with the glitch is generated; however, continuous clocks with the glitch can be

generated by setting a high-frequency for CLK_B and switching the two clocks at

the appropriate time.

The experimental jitter of the Trigger_out signal from the oscilloscope is 19.2 ns,

which accounts for 80 % of the 24 MHz LSI clock frequency. However, the construc-

tion of the glitch controller, i.e., switching two clock sources with the clock edge

timing, enables us to limit the jitter to 35 ps. This is defined by the precision of the

phase difference of the two clock sources of the pulse generator. Thus, we can inject

a fault into intermediate values using a timing violation as mentioned in Sect.

18.2

.