Information Technology Reference

In-Depth Information

reduce computational cost is to use the performance surrogate models proposed in

Section 2. As performance models are constructed as a function of selected design

parameters and parametric variations, they can be used instead of using circuit-level

simulations. Therefore, yield estimation can be achieved without large computational

cost.

One application of a variation-aware performance model is to obtain the yield-

aware Pareto fronts [23] which is best trade-offs of the overall circuit performance

and yield. In this application, in addition to searching for the general Pareto-optimal

designs, performance yield at those design points is evaluated by using the variation-

aware performance model. As a result, the yield-aware Pareto fronts can be generated.

An illustration is shown in Fig. 12. P

1

and P

2

are the performance parameters to trade-

off, and the curves are the Pareto fronts with different yield levels. The yield-aware

Pareto fronts of sub-blocks could be further used in yield-aware system design.

5.2

Surrogate-Based Circuit Optimization

Simulation-based circuit optimization is a very good application of surrogate

modeling, as the process requires a great number of iterative evaluations of objective

functions. In an optimization process, surrogate models are used to guide the search

instead of achieving the global accuracy.

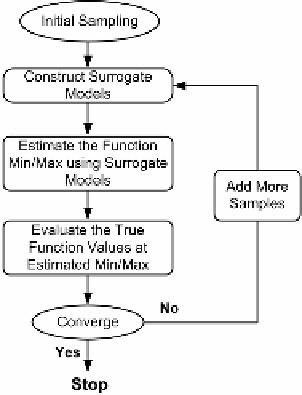

In the surrogate-based optimization process, generally there are two types of simu-

lation models, a low-fidelity and a high-fidelity model. In our circuit design problems,

the transistor-level circuit simulation is used as a high-fidelity model while the built

surrogate model is used as the low-fidelity model. The general surrogate-based opti-

mization process is shown in Fig. 13 [24].

Fig. 13.

General surrogate-based optimization flow

Search WWH ::

Custom Search