Information Technology Reference

In-Depth Information

variability of the process parameters of this transistor may push the design outside of

the specification range. In this case, information presented in Fig.11 (a)—(c) can be

used to change the matching network of the amplifier such that it can yield the desired

design metrics in all cases of process variability.

Finally, it should be noted that surrogate model-based device modeling is not li-

mited to one single design quantity. Response surface models of other important de-

sign metrics can also be developed by using the methodology described here. As an

example, consider the bandwidth of a single-stage amplifier. The bandwidth is both a

function of process parameters used in

g

m

modeling and a function of the junction

capacitances of the transistor. However, these junction capacitances depend also on

some process parameters. The exact relationships can be quantified by analytical ex-

pressions as given in the device model equations [19]. Once the additionally required

parameters are determined, then the surrogate modeling process can be applied as in

g

m

modeling.

5

Surrogate Model-Based Circuit Design

5.1

Yield-Aware Circuit Optimization

As IC technologies scale down to 65 nm and beyond, it is more challenging to create

reliable and robust designs in the presence of large process (P) and environmental

variations (e.g. supply voltage (V), temperature (T)) [22]. Without considering PVT

fluctuations, the optimal circuit design would possibly minimize the cost functions by

pushing many performance constraints to their boundaries, and result in a design that

is very sensitive to process variations. Therefore, we need to not only search for the

optimal case at the nominal conditions, but also carefully consider the circuit robust-

ness in the presence of variations. However, the fulfillment of all these requirements

introduces more complications in circuit design.

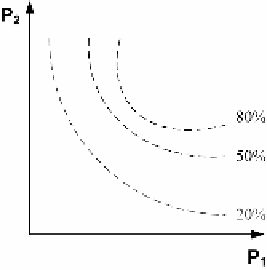

Fig. 12.

Illustration of Pareto fronts with different yield levels

Yield is defined as the number of dies per wafer that meet all predefined perfor-

mance metrics. Monte Carlo analysis of a circuit is an important technique used for

yield estimation. However, this method requires a large number of sampling points to

achieve sufficient accuracy and therefore it is very time-consuming. One solution to

Search WWH ::

Custom Search