Hardware Reference

In-Depth Information

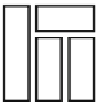

SH-X3 Cluster

SH-X3 Core3

SH-X3 Core2

SH-X3 Core1

SH-X3 Core0

CPU

SNC: Snoop Controller (Cntl.)

DAA: Duplicated Address Array

CRU:Cache RAM Control Unit

I$/D$: Instruction (Inst.)/Data Cache

IL/DL: Inst./Data Local Memory

URAM: User RAM

DBG: Debug Module

GCPG/LCPG: Global/Local CPG

INTC: Interrupt Cntl.

SHPB,HPB: Peripheral Bus Bridge

CSM: Centralized Shared Memory

DMAC: Direct Memory Access Cntl.

PCIe: PCIexpress Interface (i/f)

SCIF: Serial Communication i/f

GPIO: General Purpose IO

TMU: Timer Unit

CRU

FPU

IL

I$

D$

DL

URAM

DBG

On-chip system bus (SuperHyway)

HPB

Fig. 4.4

Block diagram of RP-1

4.2.2

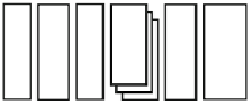

SH-X3 Cluster

The four SH-X3 cores constitute a cluster sharing an SNC and a DBG to support

symmetric-multiprocessor (SMP) and multicore-debug features. The SNC has a

duplicated address array (DAA) of data caches of all the four cores and is connected

to the cores by a dedicated snoop bus separated from the SuperHyway to avoid both

deadlock and interference by some cache coherency protocol operations. The DAA

minimizes the number of data cache accesses of the cores for the snoop operations,

resulting in the minimum coherency maintenance overhead. Each core can operate

at different CPU clock (ICLK) frequencies and can stop individually to minimize

the power (see Sect.

4.2.3

). The coherency protocol was optimized to avoid the

interference that results from a slow core to a fast core (see Sect.

4.2.4

).

4.2.3

Dynamic Power Management

Each core can operate at different CPU clock (ICLK) frequencies and can stop indi-

vidually, while the other processors are running with a short switching time in order

to achieve both the maximum processing performance and the minimum operating

power for various applications. A data cache coherency is maintained during opera-

tions at different frequencies, including frequencies lower than the on-chip system

bus clock (SCLK). The following four schemes make it possible to change each

ICLK frequency individually while maintaining data cache coherency:

1. Each core has its own clock divider for an individual clock frequency change.

2. A handshake protocol is executed before the frequency change to avoid conflicts

in bus access, while keeping the other cores running.

Search WWH ::

Custom Search