Hardware Reference

In-Depth Information

Table 3.17

Performance of MX-1

Process technology

90 nm 7Cu CMOS low standby process

Core size

3.1 mm

2

Operation frequency

200 MHz@1.2v

Power consumption

250 mW

Maximum performance

40GOPS

(16b addition)

3.6GOPS

(Fixed point signed 16bit MAC)

H-Ch0

H-Ch1

4b ALU

V-Ch

-8x

-4x

0

4x

8x

Mux

-2x

-x

0

x

2x

Adder

XREG

[3:0]

Booth

Encoder

0

[3:2]

Booth

Encoder

1

[1:0]

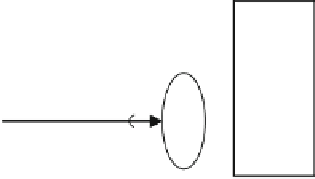

Fig. 3.70

Circuit diagram of 4-bit-grained PE

3.3.2

MX-2

The required performance of image processing is getting higher and higher; there-

fore, the second version of MX core (MX-2), which architecture is improved from the

MX-1, is developed [

63

]. The main technologies for the enhancement are men-

tioned below:

1. Expanding the processor elements from 2-bit grained to 4-bit grained

2. Improving the pipeline architecture of the MX controller

3. Equipping double frequency mode

Hereafter, these technologies are described in detail.

Figure

3.70

shows a block diagram of the PE of the MX-2. The PE contains a

4-bit temporary register (XREG) and 4-bit-grained ALU. The XREG loads data from

data registers through Horizontal channel (H-ch0, H-ch1) or Vertical channel (V-ch).

The PE loads data from data registers and through H-ch0 or H-ch1 and operates

Search WWH ::

Custom Search