Hardware Reference

In-Depth Information

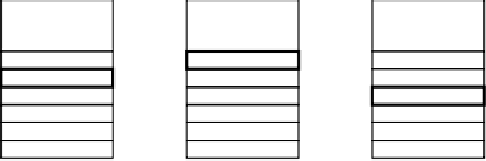

Linear address

10

10

12

Bits

DIR

PAGE

OFF

(a)

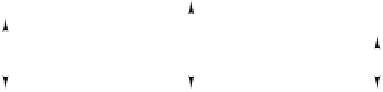

Page directory

Page table

Page frame

Word selected

PAGE

DIR

OFF

(b)

Figure 6-15.

Mapping of a linear address onto a physical address.

In Fig. 6-15(a) we see a linear address broken up into three fields:

DIR

,

PAGE

,

and

OFF

. The

DIR

field is first used as an index into the page directory to locate a

pointer to the proper page table. Then the

PAGE

field is used as an index into the

page table to find the physical address of the page frame. Finally,

OFF

is added to

the address of the page frame to get the physical address of the byte or word ad-

dressed.

The page table entries are 32 bits each, of which 20 contain a page-frame num-

ber. The remaining bits contain access and dirty bits, set by the hardware for the

benefit of the operating system, protection bits, and other utility bits.

Each page table has entries for 1024 4-KB page frames, so a single page table

handles 4 megabytes of memory. A segment shorter than 4M will have a page di-

rectory with a single entry, a pointer to its one and only page table. In this way, the

overhead for short segments is only two pages, instead of the million pages that

would be needed in a one-level page table.

To avoid making repeated references to memory, the Core i7 MMU has special

hardware support to look up the most recently used

DIR

PAGE

combinations

quickly and map them onto the physical address of the corresponding page frame.

Only when the current combination has not been used recently are the steps shown

in Fig. 6-15 actually carried out.

A little thought will reveal the fact that when paging is used, there is really no

point in having the

BASE

field in the descriptor be nonzero. All that

BASE

does is

cause a small offset to use an entry in the middle of the page directory, instead of at

the beginning. In truth, the real reason Intel included

BASE

at all is to allow pure

−