Hardware Reference

In-Depth Information

(nonpaged) segmentation, and for backward compatibility with the old 80286,

which did not have paging.

It is also worth mentioning that if a particular application does not need seg-

mentation, but is content with a single, paged, 32-bit address space, that is easy to

obtain. All the segment registers can then be set up with the same selector, whose

descriptor has

BASE

0 and

LIMIT

set to the maximum. The instruction offset will

then be the linear address, with only a single address space used—in effect, tradi-

tional paging.

We are now finished with our treatment of virtual memory on the Core i7. We

have looked only at a small (but commonly used) part of the Core i7 virtual memo-

ry system; the motivated reader can delve into the Core i7's documentation to also

learn about the 64-bit virtual address extensions and support for virtualized physi-

cal address spaces. However before leaving the topic, it is worth saying a few

words about protection, since this subject is intimately related to the virtual memo-

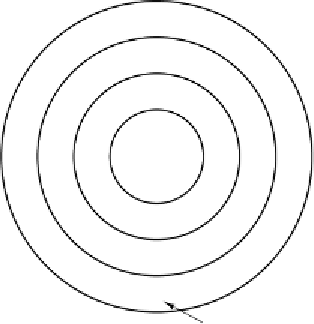

ry. The Core i7 supports four protection levels, with level 0 being the most privi-

leged and level 3 the least. These are shown in Fig. 6-16. At each instant, a run-

ning program is at a certain level, indicated by a 2-bit field in its

PSW

(

Program

Status Word

), a hardware register that holds the condition codes and various other

status bits. Furthermore, each segment in the system also belongs to a certain

level.

=

Possible uses of

the levels

p

Kernel

0

1

2

3

Level

Figure 6-16.

Protection on the Core i7.

As long as a program restricts itself to using segments at its own level, every-

thing works fine. Attempts to access data at a higher level are permitted. Attempts

to access data at a lower level are illegal and cause traps. Attempts to call proce-

dures at a different level (higher or lower) are allowed, but in a carefully controlled

way.

In order to make an interlevel call, the

CALL

instruction must contain a