Hardware Reference

In-Depth Information

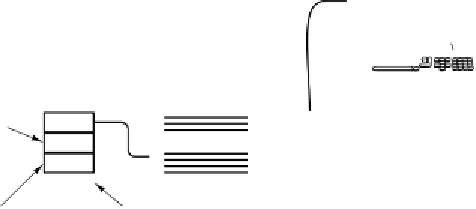

Terminal

Address

CPU

DMA

Memory

Count

100

32

4

1

RS232C

Controller

100

Device

Direction

Bus

Figure 5-32.

A system with a DMA controller.

the DMA controller increments its address register by 1 and decrements its count

register by 1. If the count register is still greater than 0, another byte is read from

memory and then written to the device.

When the count finally goes to 0, the DMA controller stops transferring data

and asserts the interrupt line on the CPU chip. With DMA, the CPU only has to in-

itialize a few registers. After that, it is free to do something else until the complete

transfer is finished, at which time it gets an interrupt from the DMA controller.

Some DMA controllers have two, or three, or more sets of registers, so they can

control multiple simultaneous transfers.

While DMA greatly relieves the CPU from the burden of I/O, the process is

not totally free. If a high-speed device, such as a disk, is being run by DMA, many

bus cycles will be needed, both for memory references and device references. Dur-

ing these cycles the CPU will have to wait (DMA always has a higher bus priority

than the CPU because I/O devices frequently cannot tolerate delays). The process

of having a DMA controller take bus cycles away from the CPU is called

cycle

stealing

. Nevertheless, the gain in not having to handle one interrupt per byte (or

word) transferred far outweighs the loss due to cycle stealing.

In this section and the next two, we will look at the instruction sets of our three

example machines: the Core i7, the OMAP4430 ARM CPU, and the ATmega168

AVR. Each has a core of instructions that compilers normally generate, plus a set